# SOLAR

## UNITÉS CENTRALES

Caractéristiques générales

Description des instructions

## AVANT PROPOS

## UNITÉS CENTRALES

## MANUEL DE RÉFÉRENCE

Ce Manuel de Référence décrit les unités centrales de la série SOLAR ; il comprend la description de toutes les instructions de la série sauf celles des options DAP16, VSS16 et FFM16.

Il ne donne que les renseignements utiles à la programmation de ces unités centrales.

La programmation des entrées-sorties se fait normalement par l'intermédiaire du programme IOCS (cf. Manuel de Référence IOCS, Manuels de Référence des systèmes, Handbook SOLAR 16). Les entrées-sorties sont traitées ici sans tenir compte des particularités relatives aux différents périphériques. Si l'on n'utilise pas IOCS, le présent manuel est donc insuffisant pour permettre la programmation des entrées-sorties.

Ce manuel sera utilisé en complément du Handbook SOLAR16, lorsque des précisions supplémentaires seront nécessaires. En raison de son organisation et de la nécessité de fournir le maximum de détails sur chacun des points abordés il n'est pas adapté à une première étude de la série SOLAR.

( ) : s'applique uniquement au processeur X

( ) : ne s'applique pas au processeur X

Sauf spécifications contraires, les caractéristiques des processeurs suivants sont identiques :

- 16-04 identique au 16-05

- 16-30 et 16-35 identiques au 16-40

- 16-70 et 16-75 identiques qu 16-65.

Le modèle 85 est un modèle commercial mono en bi-processeur constitué d'unités de traitement 75P.

Le modèle 90 est un modèle commercial mono en bi-processeur constitué d'unités de traitement 16-70.

△ en haut de page indique le changement complet de la page

par rapport à l'IE précédent

I en marge indique la partie modifiée par rapport à l'IE précédent

1 - REPRÉSENTATION DES NOMBRES

|                                                          |     |

|----------------------------------------------------------|-----|

| 1.1 - NOMBRES ENTIERS ALGEBRIQUES                        | 1-1 |

| 1.1.1 - Signification du débordement                     | 1-2 |

| 1.1.2 - Signification du report                          | 1-2 |

| 1.1.3 - Débordement dans le Cas d'une addition           | 1-2 |

| 1.1.4 - Débordement dans le Cas d'une soustraction       | 1-3 |

| 1.1.5 - Débordement dans le cas d'un changement de signe | 1-3 |

| 1.1.6 - Report dans la cas d'un changement de signe      | 1-3 |

| 1.2 - NOMBRES ENTIERS POSITIFS                           | 1-3 |

| 1.2.1 - Signification du débordement                     | 1-3 |

| 1.2.2 - Signification du report                          | 1-3 |

| 1.2.3 - Report dans la Cas d'une addition                | 1-4 |

| 1.2.4 - Report dans le Cas d'une soustraction            | 1-4 |

| 1.3 - NOMBRES FLOTTANTS                                  | 1-4 |

| 1.3.1 - Nombres flottants simple précision               | 1-4 |

| 1.3.2 - Nombres flottants double précision               | 1-8 |

| 1.3.3 - Débordement des nombres flottants                | 1-7 |

2 - REGISTRES ACCESSIBLES PAR PROGRAMME

|     |                                                         |     |

|-----|---------------------------------------------------------|-----|

| A   | - Registre accumulateur                                 | 2-1 |

| B   | - Extension de l'accumulateur                           | 2-1 |

| X   | - Registre index                                        | 2-1 |

| Y   | - Registre intermédiaire                                | 2-1 |

| C   | - Base commune                                          | 2-2 |

| L   | - Base locale                                           | 2-2 |

| W   | - Base de travail                                       | 2-2 |

| K   | - Pointeur de pile                                      | 2-2 |

| P   | - Pointeur d'instruction                                | 2-3 |

| S   | - Registre d'état de tâche                              | 2-3 |

| SLO | - Origine de la translation et de la protection mémoire | 2-4 |

| SLE | - Fin de la protection mémoire                          | 2-4 |

| ST  | - Registre d'état du processeur de traitement           | 2-4 |

| IM  | - Masque sélectif des interruptions                     | 2-5 |

| HV  | - Registre vecteur des tâches immédiates                | 2-5 |

3 - CLASSES D'INSTRUCTION, ADRESSAGE

|                                                 |     |

|-------------------------------------------------|-----|

| 3.1 - FORMAT DES INSTRUCTIONS                   | 3-1 |

| 3.2 - INSTRUCTIONS AVEC OPÉRANDE EN MEMOIRE     | 3-2 |

| 3.3 - INSTRUCTIONS DE SAUT                      | 3-3 |

| 3.4 - INSTRUCTION AVEC OPERANDE IMMEDIAT 9 BITS | 3-3 |

| 3.5 - INSTRUCTION AVEC OPÉRANDE IMMEDIAT 8 BITS | 3-3 |

| 3.6 - INSTRUCTIONS REGISTRE-REGISTRE            | 3-3 |

| 3.7 - DECALAGES ET OPERATIONS SUR BIT           | 3-4 |

| 3.8 . EXTENSIONS                                | 3-6 |

| 3.8.1 - Généralités                             | 3-4 |

| 3.8.2 - Virgule flottante simple précision      | 3-4 |

|                                                   |     |

|---------------------------------------------------|-----|

| 4 - INSTRUCTIONS                                  | 4-1 |

| 5 - TACHES IMMÉDIATES (interruptions et alarmes)  |     |

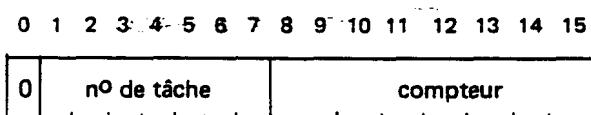

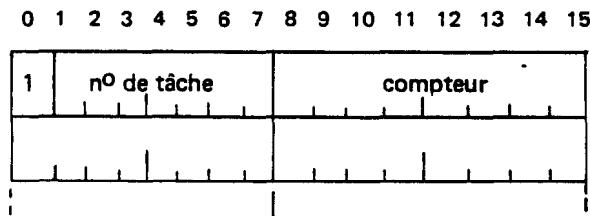

| 5.1 - MÉCANISMES GÉNÉRAUX                         | 5-1 |

| 5.1.1 - Hiérarchie                                | 5-1 |

| 5.1.2 - Election                                  | 5-1 |

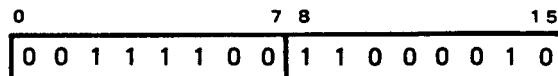

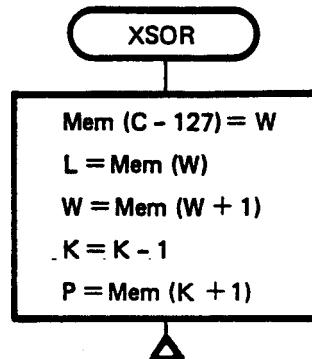

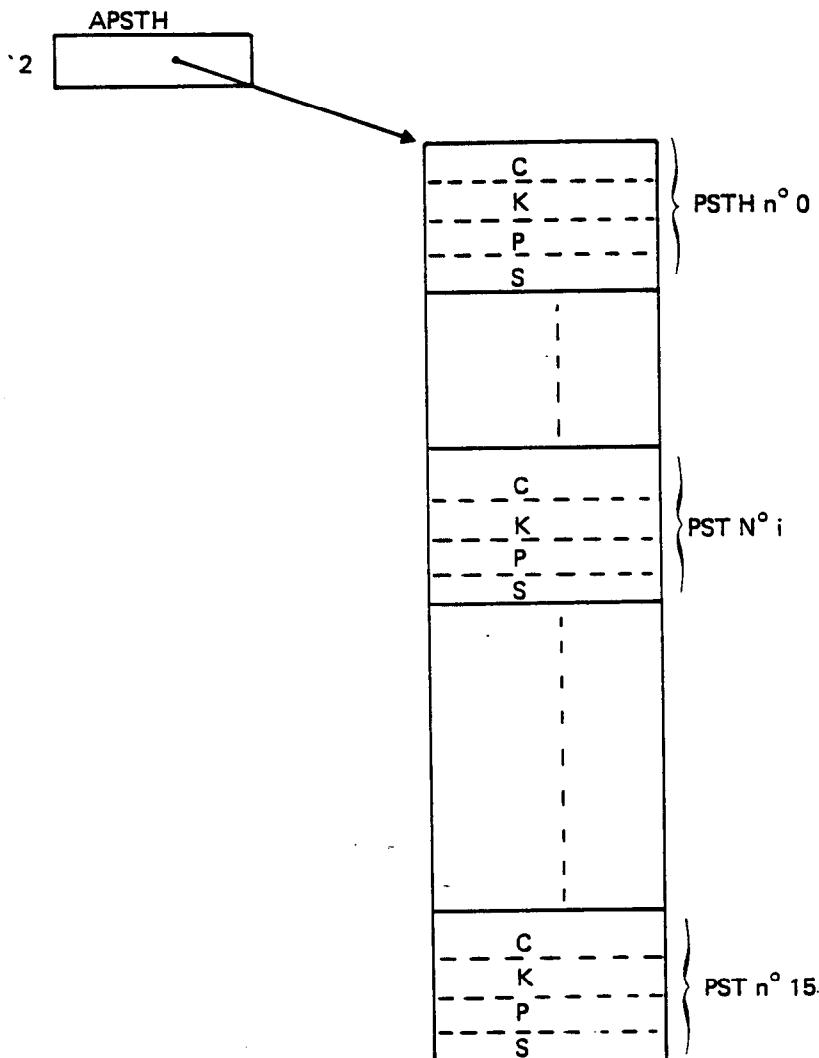

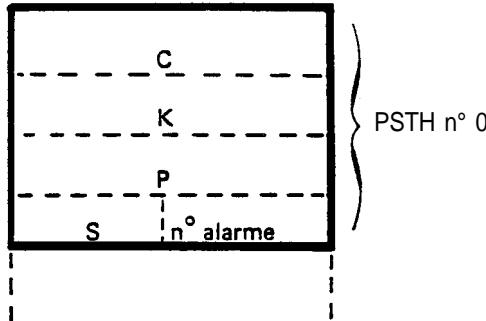

| 5.1.3 - Changement de contexte : PSTH             | 5-1 |

| 5.1.4 - Registre HV                               | 5-3 |

| 5.1.5 - Acquittement des tâches immédiates : ACQ  | 5-3 |

| 5.1.6 - Masquage                                  | 5-3 |

| 5.1.7 - Interruptibilité                          | 5-4 |

| 5.2 - TACHES D'INTERRUPTION (niveau 1 à 15)       | 5-4 |

| 5.2.1 - Sous-niveau : ACK                         | 5-4 |

| 5.2.2 - Acquittement de l'interruption            | 5-5 |

| 5.2.3 - Structure d'une tâche d'interruption      | 5-5 |

| 5.3 - TACHE ALARME                                | 5-5 |

| 5.3.1 - Généralités                               | 5-5 |

| 5.3.2 - Liste des alarmes                         | 5-6 |

| 5.4 - TACHE DEFAUT SECTEUR ET RELANCE AUTOMATIQUE | 5-7 |

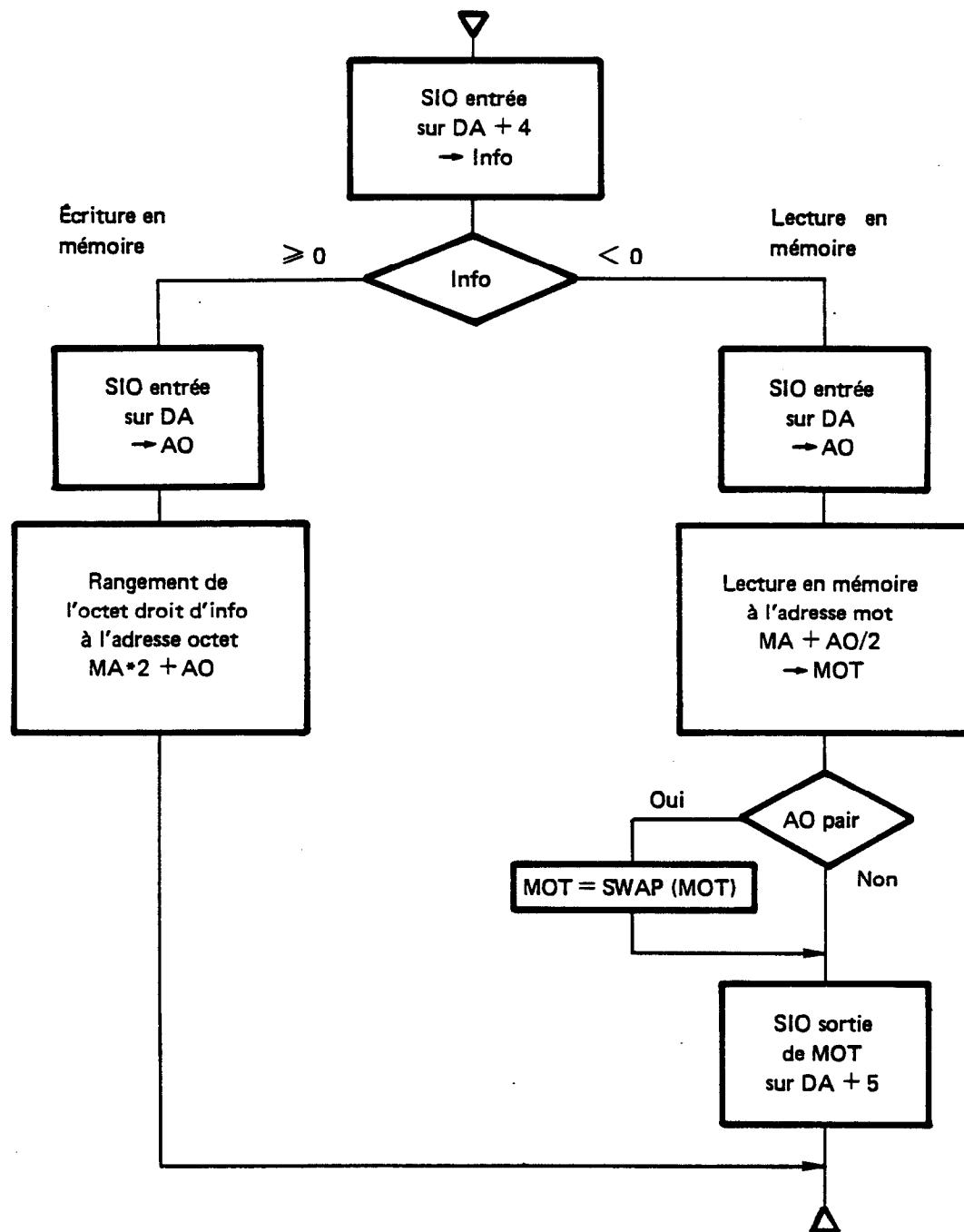

| 6 - ENTREES-SORTIES                               |     |

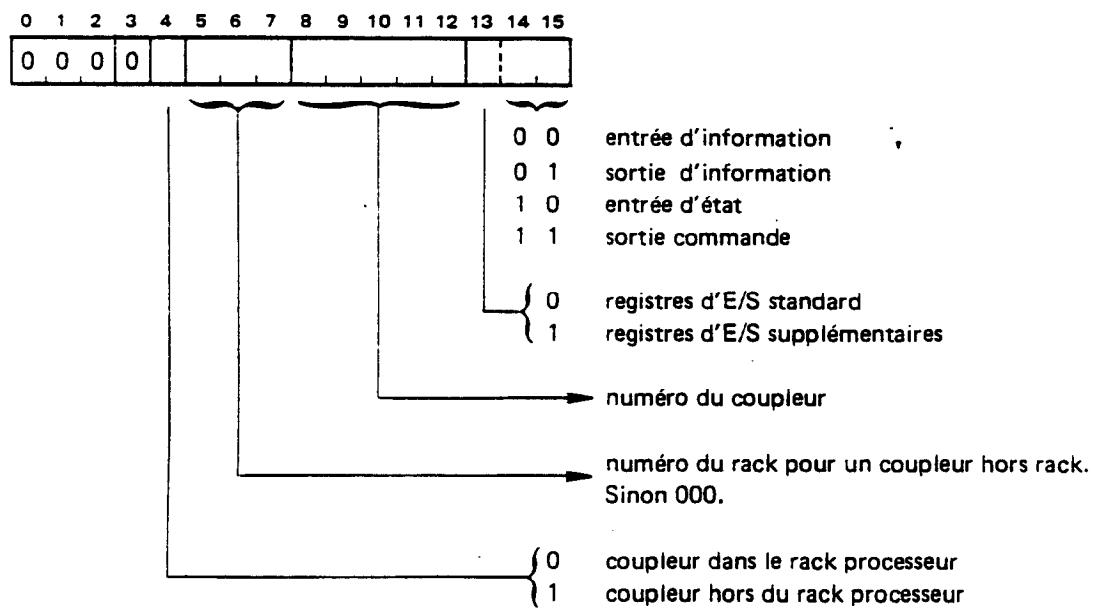

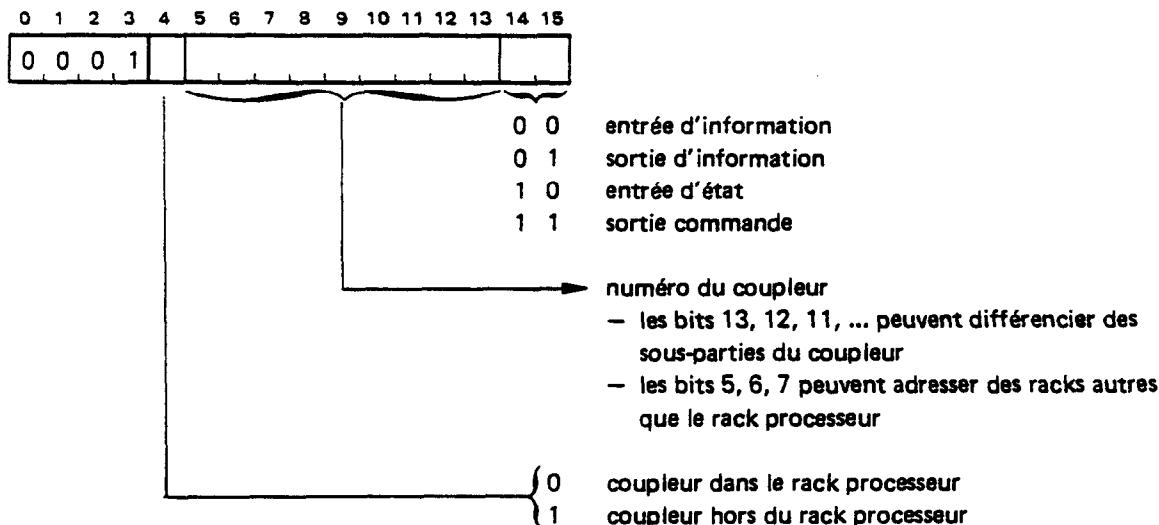

| 6.1 - GENERALITES                                 | 6-1 |

| 6.1.1 - Avertissement                             | 6-1 |

| 6.1.2 - Types de périphériques                    | 6-1 |

| 6.1.3 - Modes d'échange                           | 6-2 |

| 6.2 - NOTION DE COUPLEUR STANDARD                 | 8-2 |

| 6.2.1 - Registres d'information                   | 6-2 |

| 6.2.2 - Registres d'état                          | 6-3 |

| 6.2.3 - Registres de commande                     | 6-4 |

| 6.2.4 - Interruption normale                      | 6-5 |

| 6.2.5 - Interruption exception                    | 6-5 |

| 6.3 - PROGRAMMATION                               | 6-6 |

| 6.3.1 - Mode programme simple                     | 6-6 |

| 6.3.2 - Mode programmé prioritaire                | 6-6 |

| 6.3.3 - Mode canal                                | 6-6 |

| 7 - MISE AU POINT (mode DEBUG)                    |     |

| 7.1 - PRINCIPES GENERAUX                          | 7-1 |

| 7.2 - PUPITRE OPÉRATEUR                           | 7-1 |

| 7.3 - UTILISATION PROGRAMMEE                      | 7-2 |

| 7.4 - CANAUX                                      | 7-2 |

| 8 - OPTION DRPS (mode esclave)                    |     |

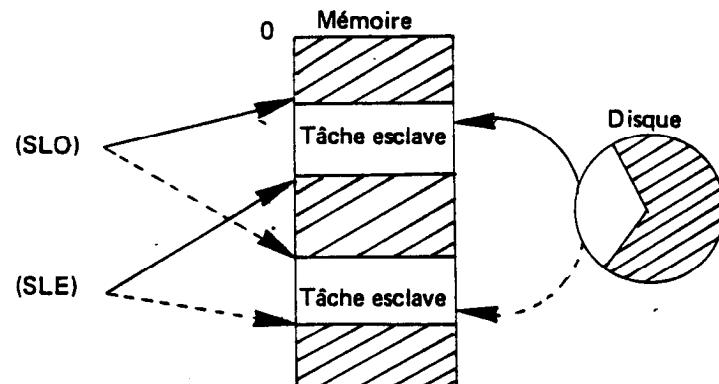

| 8.1 - PRESENTATION GENERALE                       | 8-1 |

| 8.2 - MODE ESCLAVE                                | 8-1 |

| 8.3 - TRANSLATION (SLO)                           | 8-1 |

| 8.4 - PROTECTION (SLE)                            | 8-2 |

|                                                                          |       |

|--------------------------------------------------------------------------|-------|

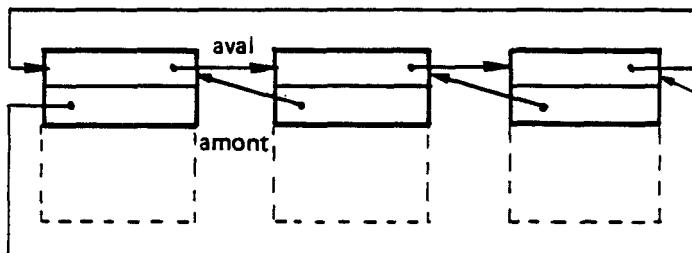

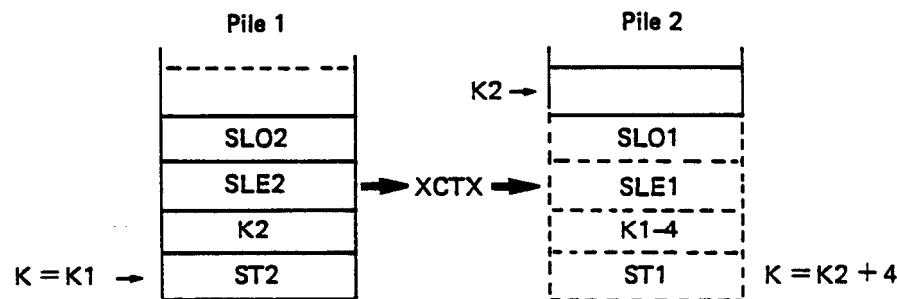

| 8.5 - COMMUNICATION ET RÉENTRANCE (pile k)                               | 8.3   |

| 8.5.1 - Esclave vers superviseur                                         | 8-3   |

| 8.5.2 - Superviseur vers esclave                                         | 8-3   |

| 8.5.3 - Esclave vers esclave                                             | 8-3   |

| 8.8 - ENTREES-SORTIES                                                    | 8-3   |

| <b>9 - OPTIONS MTS 16 : scheduler et sémaphores</b>                      |       |

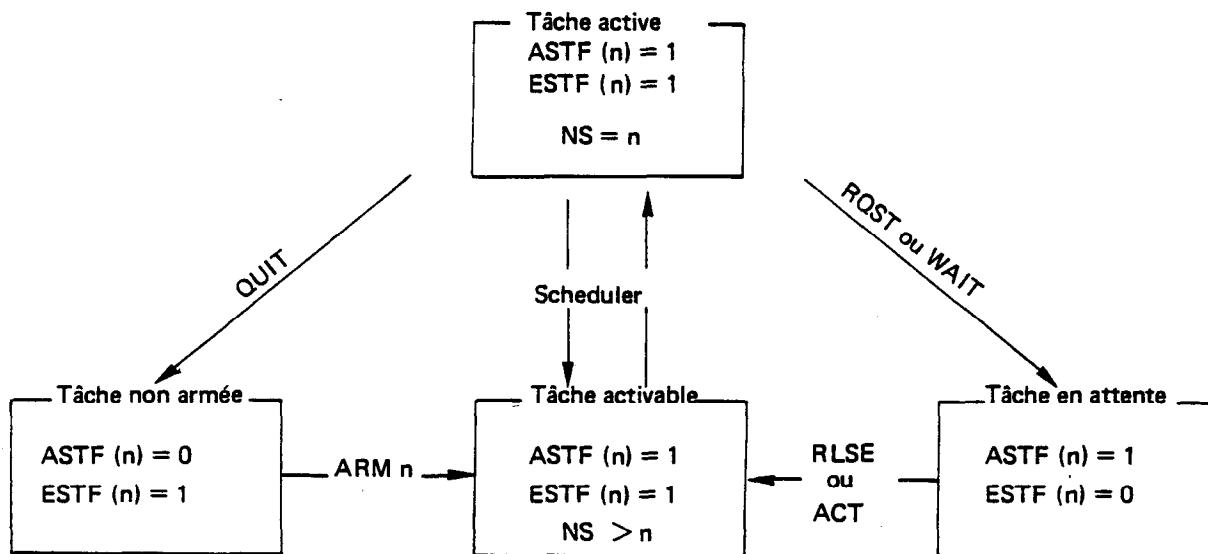

| 9.1 - TACHE DIFFEREE.                                                    | 9-1   |

| 9.1.1 - Notion                                                           | 9-1   |

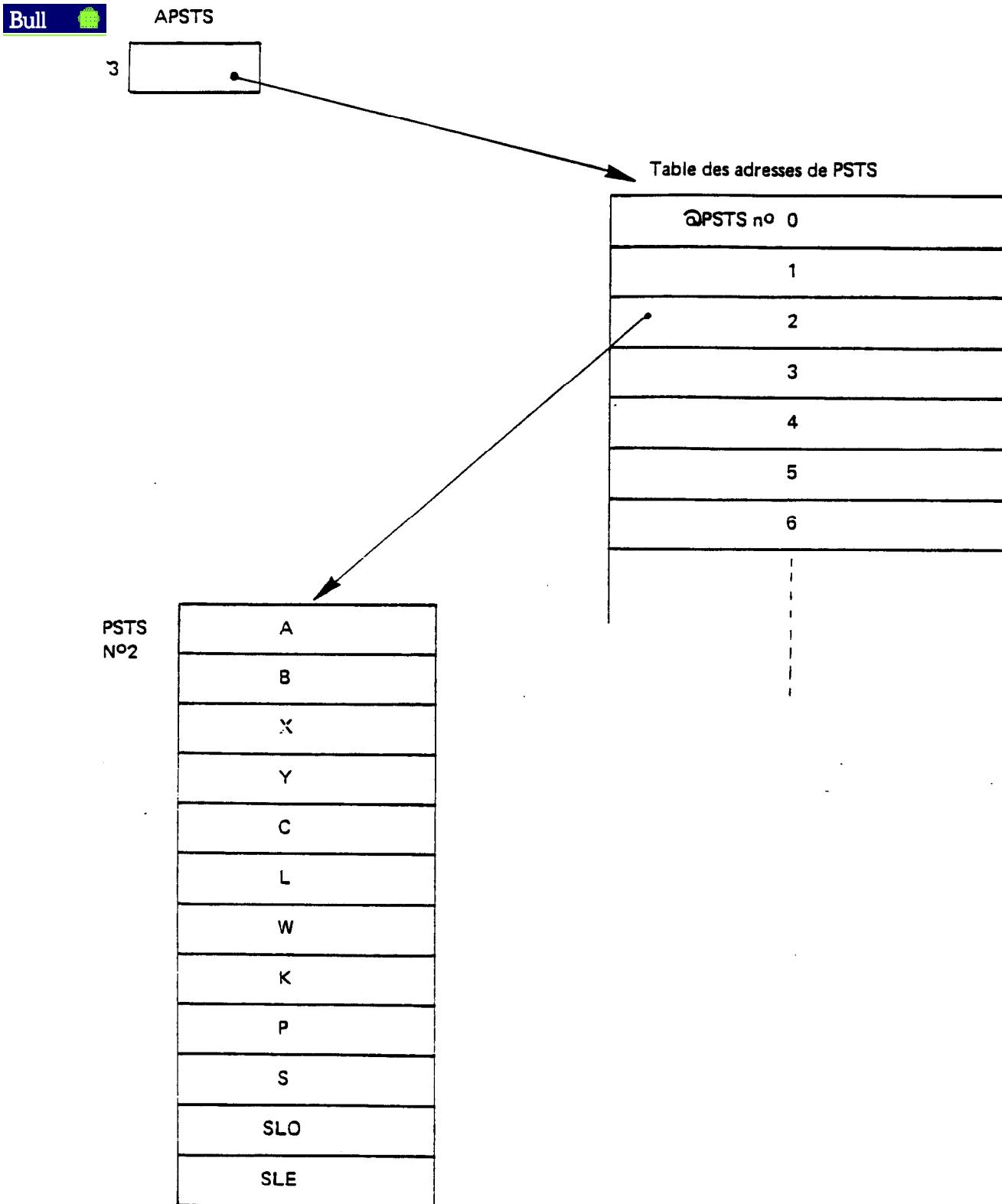

| 9.1.2 - Contexte (PSTS)                                                  | 9-1   |

| 9.2 - SCHEDULER                                                          | 9-3   |

| 9.2.1 - Hiérarchie des tâches différées                                  | 9-3   |

| 9.2.2 - File RSTF, Tache différée                                        | 9-4   |

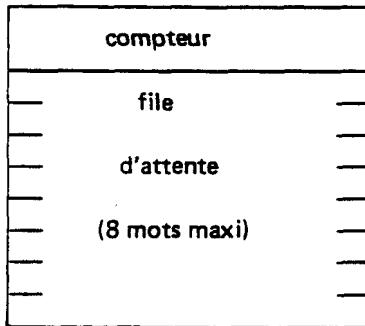

| 9.3 - SEMAPHORES D'EXCLUSION MUTUELLE : RQST, RLSE                       | 9-5   |

| 9.4 - SÉMAPHORES DE SYNCHRONISATION (privés sans paramètres) : ACT, WAIT | 9-6   |

| 9.5 - SEMAPHORES D'APPEL (privés avec paramètres) : ACT, WAIT            | 9-7   |

| <b>10 - ANNEXES</b>                                                      |       |

| CODES INSTRUCTIONS PAR ORDRE NUMÉRIQUE                                   | 10-1  |

| CODES INSTRUCTIONS PAR ORDRE ALPHABETIQUE                                | 10-3  |

| FORMAT DES INSTRUCTIONS, MODES D'ADRESSAGE                               | 10-7  |

| INSTRUCTIONS CLASSEES PAR TYPES D'OPÉRATION                              | 10-9  |

| INSTRUCTIONS PRIVILÉGIÉES (non exécutables en mode esclave)              | 10-28 |

| INSTRUCTIONS DE L'OPTION SCHEDULER-SEMAPHORES                            | 10-28 |

| INSTRUCTIONS DE L'OPTION VIRGULE FLOTTANTE SIMPLE PRECISION              | 10-28 |

| INSTRUCTIONS DIFFÉRENTES ENTRE SOLAR ET 1600                             | 10-29 |

| MEMOIRES DEBANALISÉES                                                    | 10-30 |

| TEMPS DES INSTRUCTIONS                                                   | 10-32 |

| TABLES DE CONVERSION HEXADÉCIMAL - DÉCIMAL                               | 10-46 |

| TABLE DES PUISSANCES DE 2                                                | 10-51 |

| CODAGE ASCII                                                             | 10-52 |

| CODAGE ASCII PAR ORDRE NUMERIQUE                                         | 10-56 |

## 1 - REPRÉSENTATION DES NOMBRES

|                                                                      |     |

|----------------------------------------------------------------------|-----|

| 1.1 • NOMBRES ENTIERS ALGEBRIQUES                                    | 1-1 |

| 1.1.1 • SIGNIFICATION DU DEBORDEMENT                                 | 1-2 |

| 1.1.2 • SIGNIFICATION DU REPORT                                      | 1-2 |

| 1.1.3 • DEBORDEMENT DANS LE CAS D'UNE ADDITION                       | 1-2 |

| 1.1.4 • DEBORDEMENT DANS LE CAS D'UNE SOUSTRACTION                   | 1-3 |

| 1.1.5 • DÉBORDEMENT DANS LE CAS D'UN CHANGEMENT DE SIGNE             | 1-3 |

| 1.1.6 • REPORT DANS LE CAS D'UN CHANGEMENT DE SIGNE                  | 1-3 |

| 1.2 • NOMBRES ENTIERS POSITIFS                                       | 1-3 |

| 1.2.1 • SIGNIFICATION DU DEBORDEMENT                                 | 1-3 |

| 1.2.2 • SIGNIFICATION DU REPORT                                      | 1-3 |

| 1.2.3 • REPORT DANS LE CAS D'UNE ADDITION                            | 1-4 |

| 1.2.4 • REPORT DANS LE CAS D'UNE SOUSTRACTION                        | 1-4 |

| 1.3 • NOMBRES FLOTTANTS                                              | 1-4 |

| 1.3.1 • NOMBRES FLOTTANTS SIMPLE PRECISION                           | 1-4 |

| 1.3.2 • NOMBRES FLOTTANTS DOUBLE PRECISION                           | 1-6 |

| 1.3.3 • DEBORDEMENT DES NOMBRES FLOTTANTS<br>(OVERFLOW ET UNDERFLOW) | 1-7 |

## 1.1 – NOMBRES ENTIERS ALGEBRIQUES

### Bull

Les instructions suivantes : additions (AD, ADR, ADRI, ADCR, IC), soustractions (SB, SBR, SBCR, DC), multiplications (MP), divisions (DV), changement de signe (NGR), comparaisons (CP, CPZ, CPR, CPZR, CPI), décalages numériques (SARS, SARD), permettent de faire des calculs sur des nombres binaires positifs et négatifs. Ces nombres, représentés sous la forme complément à deux, sont tels que :

- . Les nombres positifs ont toujours le bit 0 à zéro, et les nombres négatifs ont toujours le bit 0 à un. Le **bit 0 doit être interprété comme ayant le poids  $-2^{15}$  et les 15 bits poids faible comme ayant un poids positif.**

Par exemple :

$$1 \mid 111 \quad 1111 \quad 1111 \quad 1111 = (-2^{15}) + (2^{15} - 1) = -1$$

- . On change le signe d'un nombre en laissant inchangés tous les bits à partir de la droite jusqu'au premier 1 rencontré inclus, puis en inversant tous les autres bits.

Par exemple :

$$\begin{aligned} &= 0000 \quad 0000 \quad 0000 \quad 0 \mid 100 \\ &= 1111 \quad 1111 \quad 1111 \quad 1 \mid 100 \end{aligned}$$

- . Sur 16 bits ces nombres sont compris entre :

$$\begin{aligned} &- 32\,768 \text{ et } 32\,767 \\ \text{soit : } &-2^{15} \text{ et } 2^{15} - 1 \\ \text{soit : } &\text{'8000 et '7FFF en hexadécimal} \end{aligned}$$

- . Sur 32 bits ces nombres sont compris entre :

$$\begin{aligned} &- 4\,294\,967\,296 \text{ et } 4\,294\,967\,295 \\ \text{soit : } &-2^{31} \text{ et } -2^{31} - 1 \\ \text{soit : } &\text{'8000 0000 et '7FFF FFFF en hexadécimal} \end{aligned}$$

- . L'opposé du nombre négatif  $-2^{15}$  sur 16 bits et l'opposé du nombre  $-2^{31}$  sur 32 bits ne sont pas représentables.

- . Le zéro n'a qu'une seule représentation.

- . Pour attendre sur  $n + p$  bits un nombre de  $n$  bits, on le complète à gauche par  $p$  bits identiques au bit poids fort du nombre initial.

Par exemple :

'40 s'écrit '0040 sur 16 bits

'8000 s'écrit 'FFFF 8000 sur 32 bits

- . Pour réduire à  $n$  bits un nombre de  $n + p$  bits, il faut que les  $p$  bits éliminés soient tous identiques au bit poids fort du résultat

Par exemple :

'FFFF 8000 peut s'écrire '8000 sur 16 bits

'FF00 ne peut pas s'écrire sur 8 bits

- . Un nombre de  $n$  bits peut être considéré comme la somme de deux nombres : un nombre algébrique constitué par  $p$  bits poids fort suivis de  $n - p$  zéro, et un nombre positif constitué par les  $n - p$  bits poids faible.

Par exemple, en double longueur

$$\begin{aligned} \text{'FFFF FFFF} &= \text{'0000 FFFF} + \text{'FFFF 0000} \\ &= 32\,767 + (-1 \times 2^{15}) \\ &= -1 \end{aligned}$$

### 1.1.1 - SIGNIFICATION DU DÉBORDEMENT POUR LES NOMBRES ALGEBRIQUES

Lorsque les opérandes et le résultat d'une addition, d'une soustraction ou d'un changement de signe sont considérés comme des nombres algébriques, le débordement signifie que le résultat est supérieur à 32 767 ( $2^{15} - 1$ ) ou inférieur à  $-32\,768$  ( $-2^{15}$ ), donc n'est pas représentable sur 16 bits.

Le registre destination contient, après le déroulement de l'instruction, 16 bits qui sont les 16 bits poids faible du résultat algébrique correct.

### 1.1.2 - SIGNIFICATION DU REPORT POUR LES NOMBRES ALGÉBRIQUES

Le report est sans signification pour des opérandes algébriques.

### 1.1.3 – DÉBORDEMENT DANS LE CAS D'UNE ADDITION DE NOMBRES ALGÉBRIQUES

Pour AD, ADR, ADRI, ADCR le tableau suivant indique les cas où l'indicateur V (bit 6 de S) est positionné à 1.

| 1 <sup>er</sup> opérande | 2 <sup>d</sup> opérande | résultat obtenu | indicateur V | le résultat algébrique correct serait |

|--------------------------|-------------------------|-----------------|--------------|---------------------------------------|

| $\geq 0$                 | $\geq 0$                | $\geq 0$        | 0            |                                       |

| $\geq 0$                 | $\geq 0$                | $< 0$           | 1            | $> 32\,767$                           |

| $\geq 0$                 | $< 0$                   | $\geq 0$        | 0            |                                       |

| $\geq 0$                 | $< 0$                   | $< 0$           | 0            |                                       |

| $< 0$                    | $\geq 0$                | $\geq 0$        | 0            |                                       |

| $< 0$                    | $\geq 0$                | $< 0$           | 0            |                                       |

| $< 0$                    | $< 0$                   | $\geq 0$        | 1            | $< -32\,768$                          |

| $< 0$                    | $< 0$                   | $< 0$           | 0            |                                       |

#### 1.1.4 – DÉBORDEMENT DANS LE CAS D'UNE SOUSTRACTION DE NOMBRES ALGÉBRIQUES

Pour SB, SBR, SBCR le tableau suivant indique les cas où l'indicateur V (bit 6 de S) est positionné à 1 (opérande 1 - opérande 2).

| 1 <sup>er</sup> opérande | 2 <sup>d</sup> opérande | résultat obtenu | indicateur V | le résultat algébrique correct serait |

|--------------------------|-------------------------|-----------------|--------------|---------------------------------------|

| $\geq 0$                 | $\geq 0$                | $\geq 0$        | 0            |                                       |

| $\geq 0$                 | $\geq 0$                | $< 0$           | 0            |                                       |

| $\geq 0$                 | $< 0$                   | $\geq 0$        | 0            |                                       |

| $\geq 0$                 | $< 0$                   | $< 0$           | 1            | $> 32\ 767$                           |

| $< 0$                    | $\geq 0$                | $\geq 0$        | 1            | $< -32\ 768$                          |

| $< 0$                    | $\geq 0$                | $< 0$           | 0            |                                       |

| $< 0$                    | $< 0$                   | $\geq 0$        | 0            |                                       |

| $< 0$                    | $< 0$                   | $< 0$           | 0            |                                       |

#### 1.1.5 – DÉBORDEMENT DANS LE CAS DE CHANGEMENT DE SIGNE

Pour NGR : il y a débordement si l'opérande et le résultat obtenu sont de même signe, c'est-à-dire si l'opérande est égal à  $-32\ 768 (-2^{16})$

#### 1.1.6 – REPORT DANS LE CAS D'UN CHANGEMENT DE SIGNE

Pour NGR : il y a report dans tous les cas, sauf celui où l'opérande est nul

### 1.2 – NOMBRES ENTIERS POSITIFS

Alors que les opérations arithmétiques de multiplication, division, comparaisons ne peuvent être utilisées qu'avec des nombres algébriques, les instructions d'addition (AD, ADR ADRI ADCR) et de soustraction (SB, SBR, SBCR) permettent de faire aussi des calculs sur des entiers positifs. Le bit 0 ayant le poids  $2^{15}$ , ces nombres sont compris entre 0 et 65 535 ( $2^{16} - 1$ ).

Les adresses mémoire et la partie poids faible des nombres en double longueur sont des nombres absous.

#### 1.2.1 – SIGNIFICATION DU DEBORDEMENT POUR LES NOMBRES ENTIERS POSITIFS

Le débordement est sans signification pour des entiers positifs.

#### 1.2.2 – SIGNIFICATION DU REPORT POUR DES NOMBRES ENTIERS POSITIFS

Lorsque les opérandes et le résultat d'une addition ou d'une soustraction sont considérés comme des entiers positifs, le report signifie que le résultat est supérieur à 65 535 ( $2^{16} - 1$ ) dans le cas de l'addition, ou inférieur à 0 dans le cas de la soustraction, donc n'est pas représentable sur 16 bits. Le registre destination contient après le déroulement de l'instruction 16 bits qui sont les 16 bits poids faible du résultat correct.

### 1.2.3 – REPORT DANS LE CAS D'UNE ADDITION DE NOMBRES ENTIERS POSITIFS

Pour AD, ADR, ADRI, ADCR le tableau suivant indique les cas où l'indicateur C (bit 7 de S) est positionné à 1

| bit 0 du 1 <sup>er</sup><br>opérande | bit 0 du 2 <sup>d</sup><br>opérande | bit 0 du résultat<br>obtenu | Indicateur<br>C | le résultat absolu<br>correct serait |

|--------------------------------------|-------------------------------------|-----------------------------|-----------------|--------------------------------------|

| 0                                    | 0                                   | 0                           | 0               |                                      |

| 0                                    | 0                                   | 1                           | 0               |                                      |

| 0                                    | 1                                   | 0                           | 1               | > 65 535                             |

| 0                                    | 1                                   | 1                           | 0               |                                      |

| 1                                    | 0                                   | 0                           | 1               | > 65 535                             |

| 1                                    | 0                                   | 1                           | 0               |                                      |

| 1                                    | 1                                   | 0                           | 1               | > 65 535                             |

| 1                                    | 1                                   | 1                           | 1               | > 65 535                             |

### 1.2.4 – REPORT DANS LE CAS D'UNE SOUSTRACTION DE NOMBRES ENTIERS POSITIFS

Pour SB, SBR, SBCR le tableau suivant indique les cas où l'indicateur C (bit 7 de S) est positionné à 1 (opérande 1 - opérande 2).

| bit 0 du 1 <sup>er</sup><br>opérande | bit 0 du 2 <sup>d</sup><br>opérande | bit 0 du résultat<br>obtenu | indicateur<br>C | résultat absolu<br>correct |

|--------------------------------------|-------------------------------------|-----------------------------|-----------------|----------------------------|

| 0                                    | 0                                   | 0                           |                 |                            |

| 0                                    | 0                                   | 1                           |                 | < 0                        |

| 0                                    | 1                                   | 0                           |                 | < 0                        |

| 0                                    | 1                                   | 1                           |                 | < 0                        |

| 1                                    | 0                                   | 0                           |                 |                            |

| 1                                    | 0                                   | 1                           |                 |                            |

| 1                                    | 1                                   | 0                           |                 |                            |

| 1                                    | 1                                   | 1                           |                 | < 0                        |

## 1.3 - NOMBRES FLOTTANTS

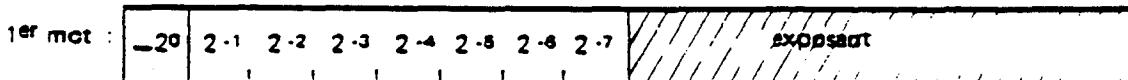

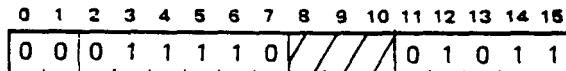

### 1.3.1 - NOMBRES FLOTTANTS SIMPLE PRECISION

L'arithmétique en virgule flottante simple précision permet de traiter des nombres algébriques dont la valeur absolue est comprise entre  $10^{-37}$  et  $10^{37}$  avec, selon les cas, 6 ou 7 chiffres significatifs.

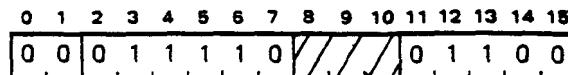

La représentation choisie pour ces nombres nécessite 32 bits. Ils occupent deux mots mémoire consécutifs ou deux registres du calculateur. Un nombre flottant est constitué d'une mantisse m de 24 bits et d'un exposant e de 8 bits. Il est interprété comme ayant la valeur  $0, m \times 2^e$ . Si le nombre est négatif la mantisse m est négative, elle est alors représentée en complément à deux.

Bull Le bit 0 de la mantisse doit être interprété comme ayant le poids  $-2^0$  et les bits suivants les poids  $+2^{-1}, +2^{-2}, \dots, +2^{-23}$ .

Si le nombre est inférieur à 1/2 en valeur absolue l'exposant est négatif, il est alors représenté en complément à deux.

Le bit 0 de l'exposant (bit 8 du premier mot) doit être interprété comme ayant le poids  $-2^7$  et les sept bits suivants les poids  $+2^6, +2^5, \dots, +2^0$ .

Les nombres positifs ont toujours le bit 0 de la mantisse à zéro, les nombres négatifs ont toujours le bit 0 de la mantisse à 1.

Les nombres flottants sont toujours normalisés, c'est-à-dire qu'ils sont tels que les deux premiers bits de la mantisse sont différents, sauf pour les nombres négatifs dont la valeur absolue est une puissance de 2.

Dans ce cas, par convention, les deux premiers bits de la mantisse sont à 1. La représentation unique utilisée pour le zéro comporte une mantisse nulle et l'exposant minimum.

- Nombre positif :

|       |       |       |         |

|-------|-------|-------|---------|

| 0 1   | ---   | ----- | [-----] |

| ----- | ----- | ----- | -----   |

- Nombre négatif (sauf puissance de 2) :

|       |       |       |         |

|-------|-------|-------|---------|

| 1 0   | ---   | ----- | [-----] |

| ----- | ----- | ----- | -----   |

- Nombre négatif puissance de 2

|         |         |                 |

|---------|---------|-----------------|

| 1 1 0 0 | 0 0 0 0 | [-----]         |

| 0 0 0 0 | 0 0 0 0 | 0 0 0 0 0 0 0 0 |

- Zéro (seule représentation utilisée)

|         |         |                   |

|---------|---------|-------------------|

| 0 0 0 0 | 0 0 0 0 | [1 0 0 0 0 0 0 0] |

| 0 0 0 0 | 0 0 0 0 | 0 0 0 0 0 0 0 0   |

Nombre flottant + 1,250 :

|         |         |                   |

|---------|---------|-------------------|

| 0 1 0 1 | 0 0 0 0 | [0 0 0 0 0 0 0 1] |

| 0 0 0 0 | 0 0 0 0 | 0 0 0 0 0 0 0 0   |

$$(2^{-1} + 2^{-3}) \times 2^{+1} = (0.5 + 0.125) \times 2$$

$$= 0.625 \times 2 = + 1,250$$

- Nombre flottant = 0,3125

$$(-2^0 + 2^{-2} + 2^{-3}) \times 2^{-1}$$

$$= (-1 + 0.25 + 0.125) \times 2^{-1}$$

$$= -0.625 \times \frac{1}{2} = -0.3125$$

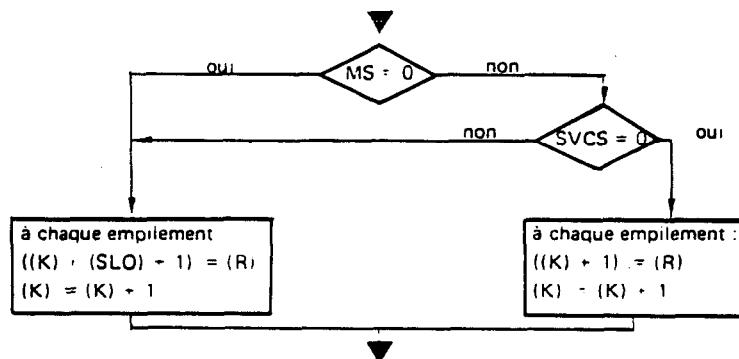

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | [ | 1 | 1 | 1 | 1 | 1 | 1 | ] |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Pour prendre l'opposé d'un nombre (changement de signe) il suffit, dans tous les cas, de prendre l'opposé de la mantisse.

Ex

nombre de départ :

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | [ | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

résultat :

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | [ | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

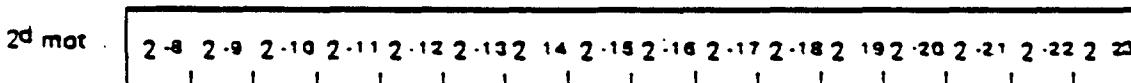

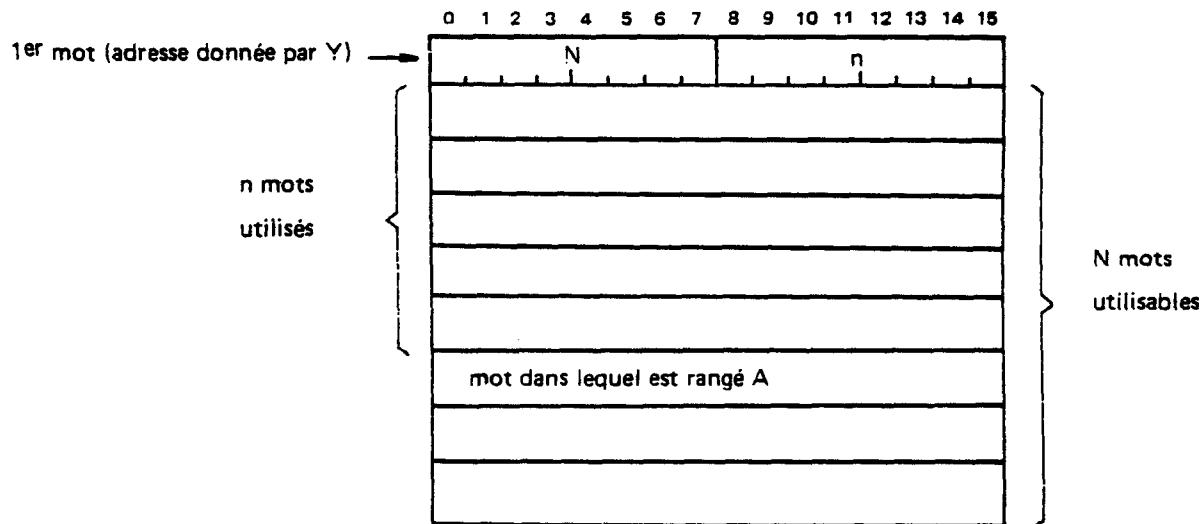

### 1.3.2 · NOMBRES FLOTTANTS DOUBLE PRECISION

L'arithmétique en virgule flottante double précision permet de manipuler des nombres algébriques dont la valeur absolue est comprise entre  $10^{-37}$  et  $10^{37}$  avec, selon le cas, 15 ou 16 chiffres significatifs.

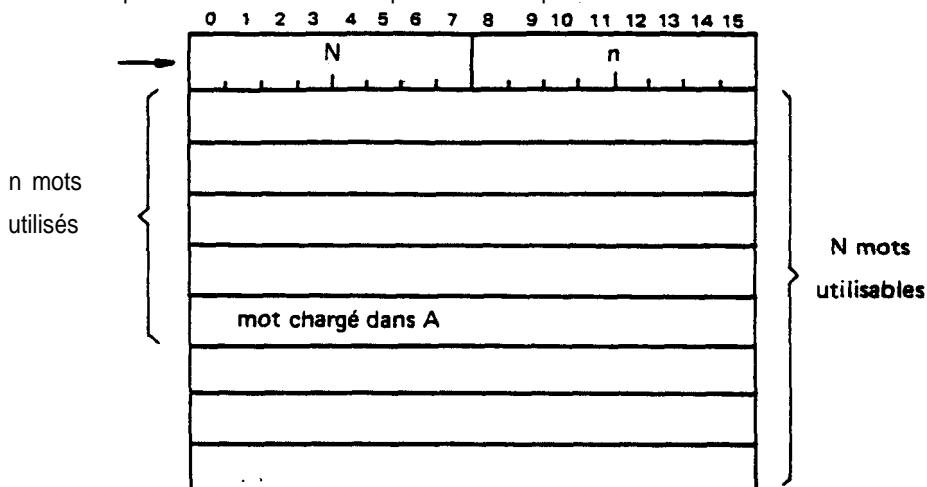

Ces nombres sont représentés sur 64 bits et occupent 4 mots mémoire consécutifs.

Le format est le suivant :

- mantisse signée sur 56 bits

- exposant signé sur 8 bits

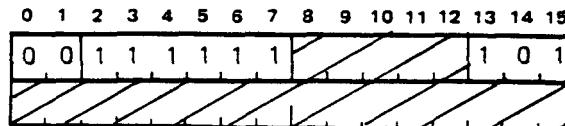

| 0                | 1               | 2   | 3 | 4   | 5               | 6               | 7 | 8 | 9   | 10               | 11 | 12 | 13 | 14 | 15 |

|------------------|-----------------|-----|---|-----|-----------------|-----------------|---|---|-----|------------------|----|----|----|----|----|

| -2 <sup>9</sup>  | 2 <sup>-1</sup> | ... | m | ... | 2 <sup>-7</sup> | 2 <sup>-6</sup> |   | e |     | 2 <sup>0</sup>   |    |    |    |    |    |

| 2 <sup>-8</sup>  | ---             |     |   | m   |                 |                 |   |   | --- | 2 <sup>-23</sup> |    |    |    |    |    |

| 2 <sup>-24</sup> | ---             |     |   | m   |                 |                 |   |   | --- | 2 <sup>-39</sup> |    |    |    |    |    |

| 2 <sup>-40</sup> | ---             |     |   | m   |                 |                 |   |   | --- | 2 <sup>-55</sup> |    |    |    |    |    |

L'exposant représente la puissance de 2

$$\text{Nb} = 0, m \times 2^e$$

Lorsque la mantisse est négative, elle est représentée en complément à 2, de même pour l'exposant.

Les règles de normalisation sont les mêmes qu'en simple précision.

Le zéro a également une seule représentation : mantisse nulle et exposant minimum

## 1.33 • DEBORDEMENT DES NOMBRES FLOTTANTS (OVERFLOW ET UNDERFLOW)

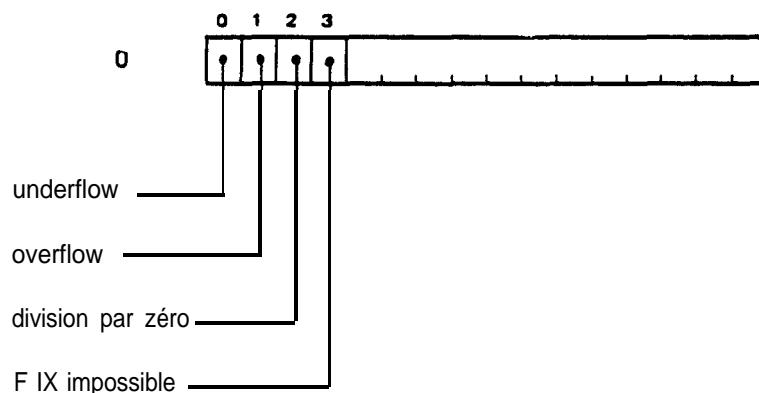

Au cours d'une addition, d'une soustraction, d'une multiplication, d'une division ou d'une normalisation, il peut se produire que l'exposant du résultat ne soit pas représentable sur 8 bits. Il y a overflow Si l'opération conduit à un résultat dont l'exposant est supérieur à 127 (nombre trop grand en valeur absolue). Dans ce cas l'indicateur V est positionné à 1

Il y a underflow si l'opération conduit à un résultat dont l'exposant est inférieur à - 128 (nombre trop petit en valeur absolue). Dans ce cas le résultat fourni est zéro et l'indicateur C est positionné à 1.

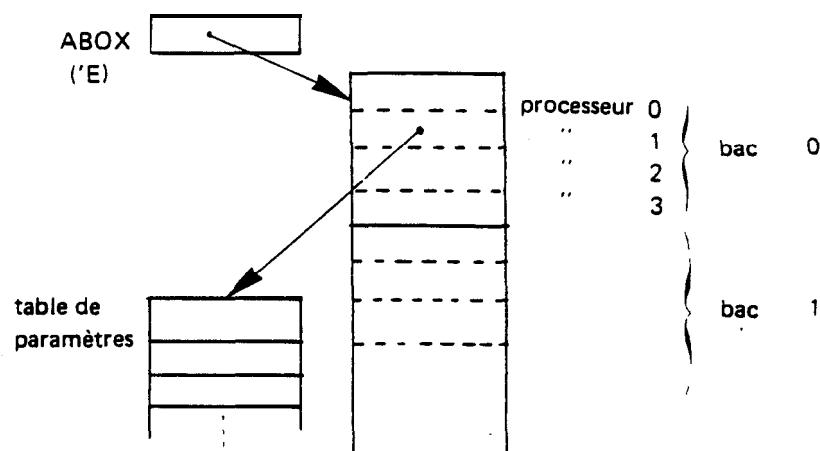

En plus de ces deux indicateurs le premier mot du COMMON (mot dont l'adresse est donnée par le contenu du registre C diminué de 128) est utilisé pour mémoriser les underflows et les overflows

le bit 0 de ce mot est mis à 1 lorsqu'il y a underflow, le bit 1 lorsqu'il y a overflow, le bit 2 lorsqu'il y a division par zéro. et le bit 3 lorsque l'opération FIX est impossible

Ces indicateurs sont rémanents, les bits correspondants n'étant jamais remis à zéro par les opérations en virgule flottante, et de cette manière il est possible de ne pas tester les indicateurs V et C après chacune des opérations en virgule flottante d'un programme.

## 2 - REGISTRES ACCESSIBLES PAR PROGRAMME

|     |                                                         |     |

|-----|---------------------------------------------------------|-----|

| A   | - REGISTRE ACCUMULATEUR                                 | 2-1 |

| B   | - EXTENSION DE L'ACCUMULATEUR                           | 2-1 |

| X   | - REGISTRE INDEX                                        | 2-1 |

| Y   | - REGISTRE INTERMEDIAIRE                                | 2-1 |

| C   | - BASE COMMUNE                                          | 2-2 |

| L   | - BASE LOCALE                                           | 2-2 |

| W   | - BASE DE TRAVAIL                                       | 2-2 |

| K   | - POINTEUR DE PILE                                      | 2-2 |

| P   | - POINTEUR D'INSTRUCTION                                | 2-3 |

| S   | - REGISTRE D'ETAT DE TACHE                              | 2-3 |

| SLO | - ORIGINE DE LA PROTECTION MEMOIRE ET DE LA TRANSLATION | 2-4 |

| SLE | - FIN DE LA PROTECTION MEMOIRE                          | 2-4 |

| ST  | - REGISTRE D'ÉTAT DU PROCESSEUR DE TRAITEMENT           | 2-4 |

| IM  | - MASQUE SELECTIF DES INTERRUPTIONS-                    | 2-5 |

| HV  | - REGISTRE VECTEUR DES TACHES IMMEDIATES                | 2-5 |

## 2 - REGISTRES ACCESSIBLES PAR PROGRAMME

### A - REGISTRE ACCUMULATEUR

A est le registre destination de la plupart des instructions ayant un mot mémoire pour opérande

A peut être chargé à partir de la mémoire ou rangé en mémoire.

A est un des registres opérandes possibles des Instructions registre-registre

A est le registre qui sert aux échanges avec les périphériques.

A est sauvegardé et restaure lors des changements de contextes de tâches différées.

### B - EXTENSION DE L'ACCUMULATEUR

B sert d'extension à l'accumulateur et constitue avec celui-ci un registre 32 bits

- pour des opérandes arithmétiques en double longueur (multiplication, division, décalage numérique)

- pour des opérandes logiques en double longueur (décalages logiques et circulaires, opérations sur bits)

- pour les opérandes en virgule flottante

B peut être chargé à partir de la mémoire ou rangé en mémoire

B est un des registres opérandes possibles des instructions registre-registre.

B est sauvegarde et restauré lors des changements de contextes de tâches différées.

### X - REGISTRE INDEX

X a le rôle d'index dans l'adressage indirect des opérandes mémoire : lorsqu'une constante adresse comporte le bit 0 à 1 les 16 bits de l'index sont ajoutés aux 15 bits poids faible de la constante adresse ; le contenu de X est alors considéré comme un entier algébrique.

X permet d'indexer les instructions de décalage, d'opération sur bit et l'instruction ARM : son contenu est ajouté aux bits 11 à 15 (9 à 15 pour ARM) de l'instruction.

X peut être chargé à partir de la mémoire et rangé en mémoire.

X est un des registres opérandes possibles des instructions registre-registre.

X est sauvegarde et restauré lors des changements de contextes de tâches différées.

### Y - REGISTRE INTERMEDIAIRE

Y peut être chargé à partir de la mémoire et rangé en mémoire

Y est un des opérandes possibles des instructions registre-registre.

De préférence aux registres A B et X qui ont des rôles spécifiques et qu'il est souvent intéressant de ne pas modifier, Y est destiné à servir de registre intermédiaire.

Par exemple l'utilisation de Y est conseillée pour :

- charger à partir de la mémoire ou ranger en mémoire C, L, W ou K ;

- transférer le contenu d'une mémoire dans une autre mémoire

- faire des opérations arithmétiques, logiques, de comparaison entre la mémoire et un des registres B, X, C, L, W, K sans modifier l'accumulateur.

Y est sauvegardé et restauré lors des changements de contextes différés.

#### C - BASE COMMUNE

#### L - BASE LOCALE

#### W - BASE DE TRAVAIL

C, W et L ont un fonctionnement identique. Le choix des appellations respectives de ces registres (qui correspond à l'utilisation qui en est faite dans l'assembleur et PL16) est arbitraire.

C, L et W sont utilisés en tant que bases dans l'adressage de la mémoire, les 16 bits de ces registres permettant aux instructions à référence mémoire (qui comportent l'indication d'une base et d'un déplacement sur 6 bits) d'accéder à trois zones mémoire de 256 mots chacunes.

C, L et W sont des opérandes possibles pour les instructions registre-registre.

C, L et W sont sauvegardés et restaurés lors des changements de contextes différées. Seul C est sauvegarde et restauré lors des changements partiels des tâches immédiates.

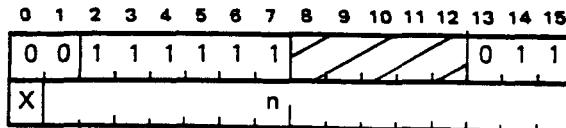

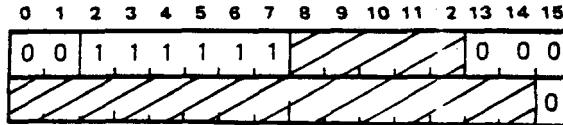

#### K - POINTEUR DE PILE

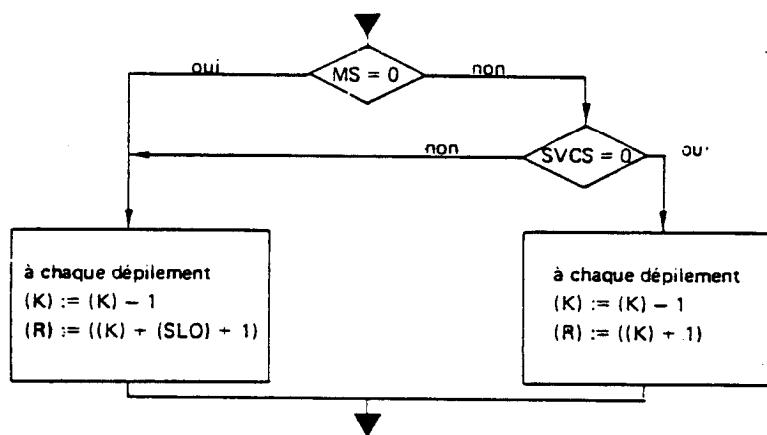

Les 16 bits de K sont utilisés pour pointer sur une zone mémoire fonctionnant en pile. Les instructions BSR et SVC utilisent cette pile pour sauvegarder le registre P, les instructions RSR et RSV pour le restaurer. De même l'instruction PSR utilise cette pile pour sauvegarder les registres A, B, X, Y, C, L, W, K et l'instruction PLR pour le restaurer.

Les instructions de sauvegarde incrémentent K avant chaque rangement et les instructions de restauration le décrémentent après chaque chargement, de telle manière qu'il pointe toujours sur la mémoire occupée de la pile d'adresse la plus grande. Si la pile est vide K pointe sur la mémoire précédant immédiatement la pile.

K est un des opérandes possibles des instructions registre-registre.

K est sauvegardé et restauré lors des changements de contextes immédiats et différés.

Il doit y avoir une pile pour chaque tâche immédiate ou différée ; en particulier, les tâches différées peuvent être mises en attente et ne se terminent donc pas toujours dans l'ordre hiérarchique des priorités.

## P - POINTEUR D'INSTRUCTION

Les 16 bits de ce registre indiquent l'adresse de la prochaine instruction à exécuter.

P est sauvegardé et restauré lors des changements de contextes de tâches immédiates et différées.

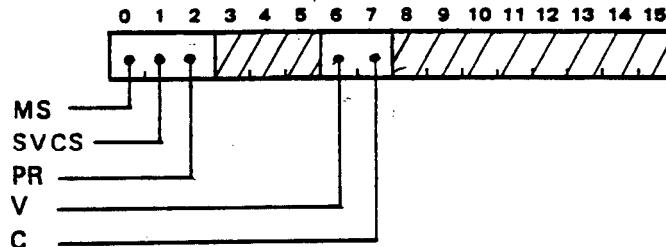

## S - REGISTRE D'ETAT DE TACHE

S est en fait le sous-ensemble des bits de ST qui appartiennent au contexte d'une tâche ; ils participent donc aux changements de contextes de tâches immédiates et différées.

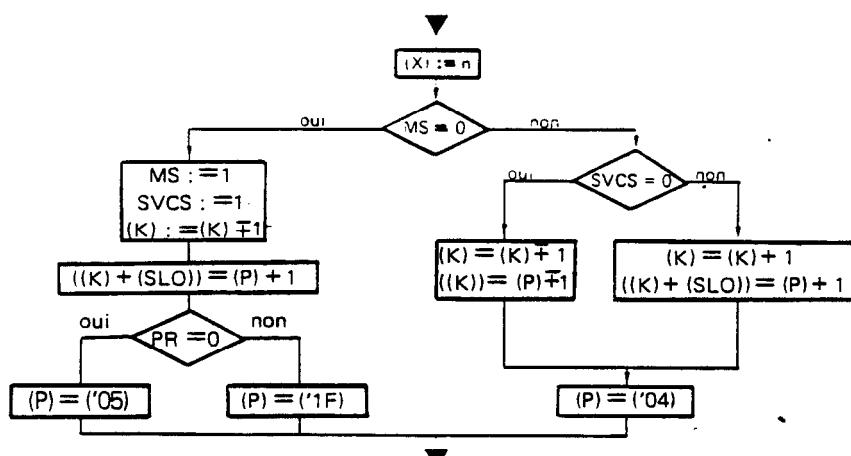

Les bits MS, SVCS et PR déterminent le mode de fonctionnement de la machine.

|              |   |   | Disponible sur SOLAR 16 |       |          |       |     |

|--------------|---|---|-------------------------|-------|----------|-------|-----|

| MS, SVCS, PR |   |   | Mode                    | 04/05 | 30/35/40 | 65/75 | 70  |

| 0            | 0 | 0 | Esclave                 | non   | oui      | oui   | oui |

| 0            | 0 | 1 | Privilégié              | non   | non      | non   | oui |

| 1            | X | X | Maître                  | oui   | oui      | oui   | oui |

Dans le cas où le mode privilégié est inexistant (Solar autre que 16-70), la position du bit PR est non significative.

Le mécanisme DRPS est :

- inexistant sur SOLAR 16-04 et 16-05

- optionnel sur SOLAR 16-40, 16-65 et 16-75

- standard sur SOLAR 16-30, 16-35 et 16-70.

Mode Esclave :

Certaines instructions sont interdites dans ce mode.

Leur exécution provoque une alarme.

Si l'option DRPS est présente, le mécanisme de translation et de protection mémoire est activé.

Mode Privilégié :

Pratiquement toutes les instructions dites privilégiées sont exécutables dans ce mode.

Si l'option DRPS est présente, le mécanisme de translation et de protection mémoire est activée.

Mode Maître :

Toutes les instructions sont exécutables dans ce mode.

Pour l'adressage normal le mécanisme de translation et de protection mémoire est inefficace.

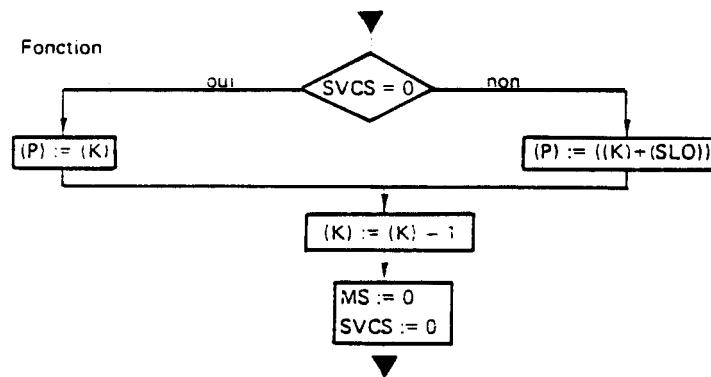

Dans ce mode, le bit SVCS permet d'activer le mécanisme de translation et protection mémoire uniquement pour les empilements et dépilements à travers K par les instructions appropriées.

Les sous-programmes superviseur peuvent ainsi accéder à la pile de l'appelant (réentrance) tout en conservant les propriétés de translation et de protection DRPS.

Dans ce mode, le bit PR permet de savoir si l'appelant est un esclave (PR = 0) ou un privilégié (PR = 1).

Indicateur V et indicateur C :

Bull

Ces deux indicateurs sont positionnés par certaines instructions, avec des significations différentes selon l'instruction, et peuvent ensuite être testés par les jumps conditionnels. (Les opérations arithmétiques, les comparaisons, les décalages, certaines instructions sur bits, etc... positionnent ces deux indicateurs).

- après une instruction arithmétique :

$V = 1$  si débordement (entiers algébriques)

$C = 1$  si report (entiers arithmétiques)

- après instruction de comparaison

$V = 1$  si les deux nombres sont égaux

$C = 1$  si le 1er terme est algébriquement inférieur au second.

L'exécution de l'instruction SCY (qui positionne l'indicateur C à 1 sans modifier l'indicateur V) est le seul cas où un des indicateurs est modifié sans que l'autre le soit.

Dans tous les autres cas ou bien l'état de chacun des deux indicateurs a une signification, ou bien seul l'un des indicateurs a une signification et l'autre est remis à zéro.

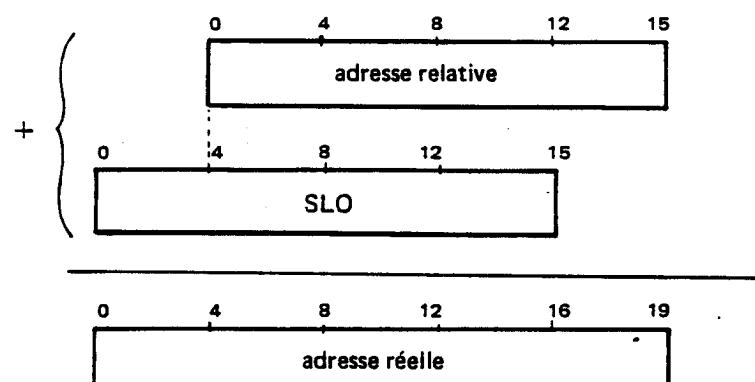

## SLO - ORIGINE DE LA PROTECTION MEMOIRE ET DE LA TRANSLATION

### SLE - FIN DE LA PROTECTION MEMOIRE

Les registres SLO et SLE font partie de l'option DRPS (donc n'existent pas sur 05)

Ces registres contiennent les 16 bits poids fort d'adresses mémoire (20 bits) qui doivent être multiples de 16.

SLO contient l'adresse physique de l'origine (adresse logique 0) d'une tâche en mode esclave.

SLE définit l'adresse physique de la fin d'une tâche en mode esclave. Vu le format de cette adresse, il pointe en fait le premier des 16 derniers mots de la tâche.

De plus, la taille d'une tâche (représentée par la différence SLE - SLO) ne doit pas excéder 64 Kmots. Les registres SLO et SLE sont accessibles par les instructions RDOE et WOE. Ils sont sauvegardés et restaurés lors d'un changement de Contexte de tâches différentes.

Si la différence SLE - SLO ne respecte pas la condition exposée ci-dessus, les 4 bits poids fort de SLE sont modifiés par le calculateur.

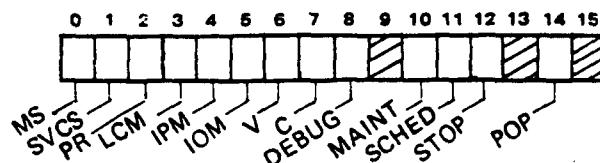

## ST - REGISTRE D'ETAT DU PROCESSEUR DE TRAITEMENT

Ce registre regroupe les différents bits qui définissent l'état du processeur à chaque instant. Il comprend d'une part des bits appartenant au Contexte d'une tâche (registre S) d'autre part des bits qui ne font pas partie du contexte des tâches et ne participent donc pas aux changements de contexte ni immédiat, ni différé.

- les bits non explicités ne sont utilisables que par la micromachine et ne doivent jamais être modifiés ni au pupitre ni par programme.

- les bits MS, SVCS, PR, V et C font partie du registre S et sont décrits à cette rubrique :

- LCM : masque des interruptions du canal LDC (1 = interruptions masquées).

- IPM : masque des interruptions interprocesseurs (05 25 1 = interruptions masquées).

- IOM : masque global des interruptions de programme y compris du défaut secteur (1 = interruptions masquées).

- DEBUG : positionné à 1, le processeur est en mode mise au point. Les erreurs de parité mémoire ne sont plus interprétées comme telles mais comme des points d'arrêt. De plus la vitesse du processeur est altérée dans un rapport variant de 1 à 3 environ.

- MAINT : ce bit est normalement à 0 ; s'il a la valeur 1, le processeur passe dans un mode spécial réservé à la maintenance. Dans ce mode les erreurs de parité ne provoquent plus ni d'alarmes ni de points d'arrêt.

- SCED : s'il est à 1, ce bit signifie que le processeur a été interrompu au cours de son passage dans le scheduler. Le bit SVCS prend pendant ce passage une autre signification :

1 = la sauvegarde du contexte de la tâche différée abandonnée n'est pas faite

0 = la sauvegarde a été faite

Cette signification est temporaire ; elle ne peut être vue au pupitre mais seulement à l'examen du contexte réduit de la tâche immédiate interrompante (registre S).

- STOP :

= 0 le processeur est en marche programme et exécute donc des instructions.

= 1 le processeur est à l'arrêt programme et ne traite que les appels canaux éventuels.

Ce bit peut être forcé à 1 par programme (instruction SST) mais l'arrêt n'est pas instantané et le processeur continue à exécuter les instructions suivantes pendant environ 2 millisecondes.

- POP

: Ce bit n'a de sens que si le processeur est en mode mise au point (DEBUG = 1) :

- 1 : mode mise au point au pupitre. Les points d'arrêt provoquent l'arrêt programme.

- 0 : mode mise au point programme. Les points d'arrêt provoquent des alarmes à traiter par programme.

A l'initialisation du calculateur,

- MS = 1 : mode maître

- LCM = IPM = IOM = 1 : toute interruption masquée

- STOP = 1 : arrêt programme (STOP = 0 en cas de RESTART).

- Les autres indicateurs sont à 0.

## IM - MASQUE SELECTIF DES INTERRUPTIONS

Les bits 1 à 15 de ce registre permettent, quand ils sont à 1 de masquer sélectivement les niveaux d'interruptions de programme 1 à 15. Les appels masqués sont mis en attente et seront pris en compte dès leur démasquage. Par contre si un niveau est masqué au cours de son traitement, soit dans sa propre tâche immédiate soit dans une tâche de niveau supérieur, ce traitement continue jusqu'à l'acquittement de sa tâche (ACQ).

Le bit 0 de IM ne masque pas la tâche alarme ; par contre il permet de masquer le pupitre opérateur. Ce masquage n'est actif qu'en marche programme ; le pupitre opérateur est toujours opérationnel quand le calculateur est à l'arrêt.

Les masques IOM et IM agissent indépendamment l'un de l'autre ; une interruption de rang i est masquée :

- soit si  $IOM_i = 1$  quelle que soit la valeur de  $IM_i$  (**masquage global**)

- soit si  $IM_i = 1$  quelle que soit la valeur de IOM (masquage sélectif).

IM ne participe à aucun changement de contexte

Le masque IM peut être modifié par l'instruction XIMR

A l'initialisation du calculateur, IM est à 0.

## HV - REGISTRE VECTEUR DES TACHES HARDWARE

Ce registre recense les différentes demandes d'interruption qui ont été prises en compte et dont le traitement n'est pas encore terminé ; à chaque tâche immédiate dans cet état correspond un bit à 1 dans HV ayant pour rang le numéro de priorité de cette tâche.

Parmi ces tâches, seule celle de plus forte priorité (rang dans HV le plus faible) est en cours d'exécution ; les autres sont suspendues jusqu'à la fin du traitement de la plus prioritaire.

HV peut être lu par programme (RDHV) mais ne peut être modifié.

HV ne fait pas partie du contexte des tâches et ne participe donc à aucun changement de contexte.

HV est à zéro à l'initialisation du calculateur.

### 3 - CLASSES D'INSTRUCTION, ADRESSAGE

|                                                 |     |

|-------------------------------------------------|-----|

| 3.1 • FORMAT DES INSTRUCTIONS                   | 3-1 |

| 3.2 • INSTRUCTIONS AVEC OPÉRANDE EN MÉMOIRE     | 3-2 |

| 3.3 • INSTRUCTIONS DE SAUT                      | 3-3 |

| 3.4 • INSTRUCTION AVEC OPERANDE IMMÉDIAT 9 BITS | 3-3 |

| 3.5 • INSTRUCTION AVEC OPERANDE IMMEDIAT 8 BITS | 3-3 |

| 3.6 • INSTRUCTIONS REGISTRE-REGISTRE            | 3-3 |

| 3.7 • DECALAGES ET OPERATIONS SUR BIT           | 3-4 |

| 3.8 • EXTENSIONS                                | 3-4 |

| 3.8.1 • GENERALITES                             | 3-4 |

| 3.8.2 • VIRGULE FLOTTANTE SIMPLE PRÉCISION      | 3-4 |

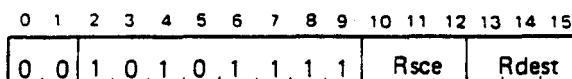

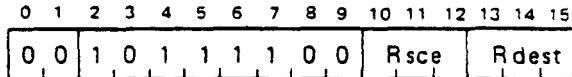

### 3.1 • FORMAT DES INSTRUCTIONS

Bull

Les instructions peuvent être, classées, selon les différents champs qui les composent, en 9 formats différents (à l'exception de PSR, PLR, SVC et ARM qui utilisent chacune un format propre).

A chacun des différents formats correspondent un ou plusieurs modes d'adressage spécifiques.

|           |       |          |                      |

|-----------|-------|----------|----------------------|

| Notations | base  | $\equiv$ | base C, L ou W       |

|           | &     | $\equiv$ | indirection          |

|           | Rsce  | $\equiv$ | registre source      |

|           | Rdest | $\equiv$ | registre destination |

- . Instructions avec opérande en mémoire (mot ou octet)

- adresage base direct, indirect, indirect post-indexé

- #### . Instructions de saut adressage par rapport à P

- . Instructions avec opérande immédiat 9 bits

adressage immédiat

- . Instructions avec opérande immédiat 8 bits

adressage immédiat

- . Instructions registre-registre

8 registres adressables en tant que registres banalisés

- . Décalages et opérations sur bits non indexés ou indexés

- #### . Instructions sans indication d'opérande

Instructions extensions (codes réservés)

exemples :

- flottant simple n = 0

- double précision n = 1

- scheduler CDA n = 7

(voir p. 4.22)

- Instructions virgule flottante sans opérande de mémoire

Ces instructions occupent deux mots de 16 bits, le premier mot identifiant l'instruction comme faisant partie de l'extension flottant

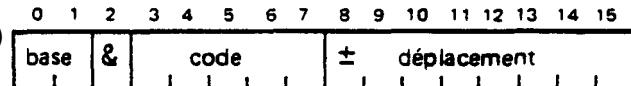

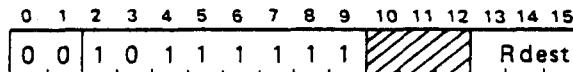

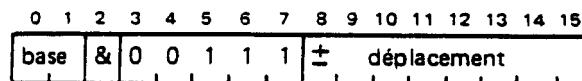

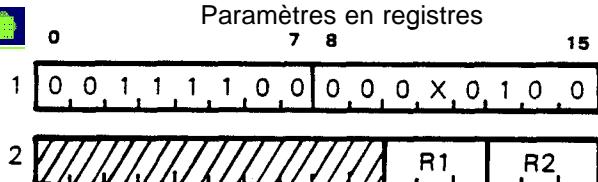

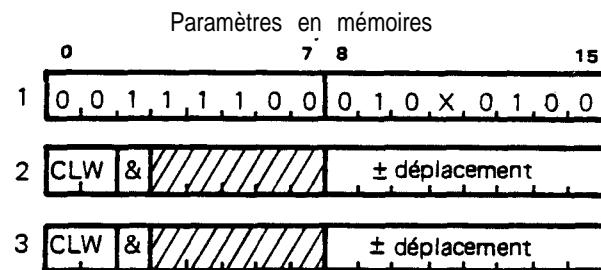

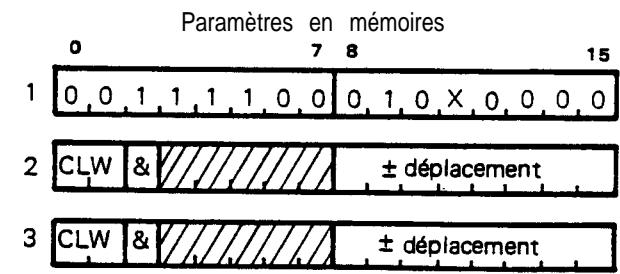

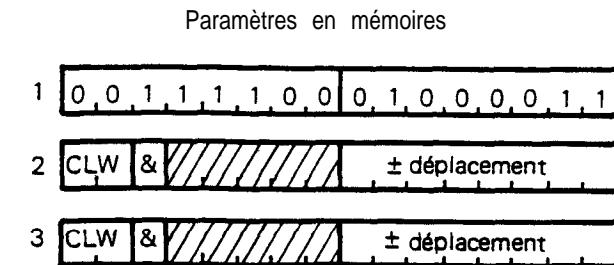

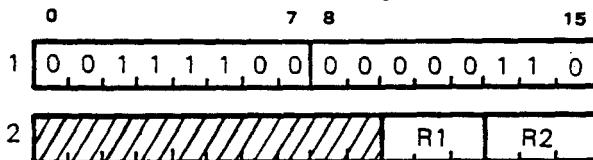

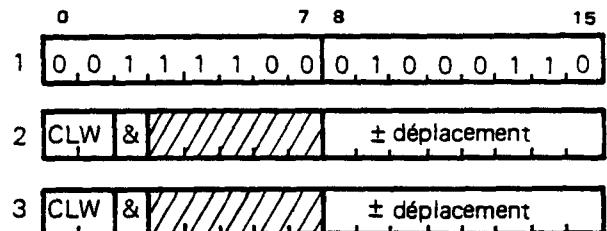

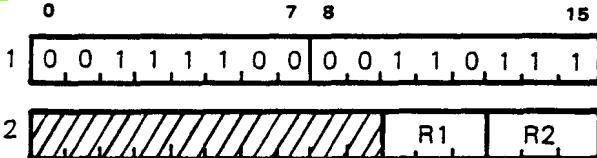

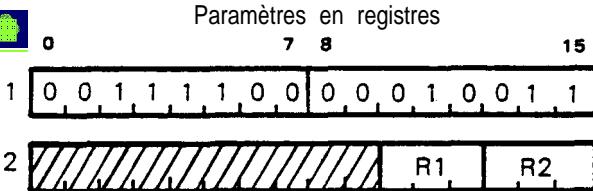

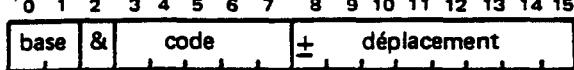

### 3.2 - INSTRUCTIONS AVEC OPERANDE EN MEMOIRE

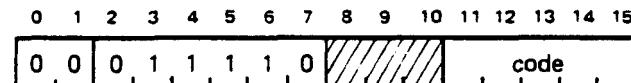

Les bits 0 et 1 comportent l'indication d'une base avec le codage indiqué ci-contre. Le bit 2, lorsqu'il est à 1, indique l'adressage indirect.

|        |    |

|--------|----|

| base C | 01 |

| L      | 10 |

| W      | 11 |

Les bits 8 à 15 comportent un déplacement compris entre - 128 et + 127. Certaines de ces instructions ont pour opérande un mot, d'autres, un octet. Elles utilisent l'adressage direct, indirect et indirect post-indexé, avec dans tous les cas l'adressage base, dont le fonctionnement est le suivant : le déplacement est additionné au contenu du registre de base indiqué par l'instruction, ce qui permet d'avoir accès à chacun des 256 mots dont l'adresse est comprise entre "valeur de la base - 128" et "valeur de la base + 127."

- Adressage direct de mot : l'opérande est le mot mémoire adressé par la base et le déplacement.

- Adressage indirect de mot : l'opérande est le mot mémoire dont l'adresse est donnée par les 15 bits poids faible d'un relais d'indirection, ce relais d'indirection étant le mot mémoire adressé par la base et le déplacement. Dans ce cas le bit 0 du relais d'indirection vaut 0. Ce mode d'adressage ne donne accès qu'à 32 K mots (adresses comprises entre SLO et SLO + 32 767).

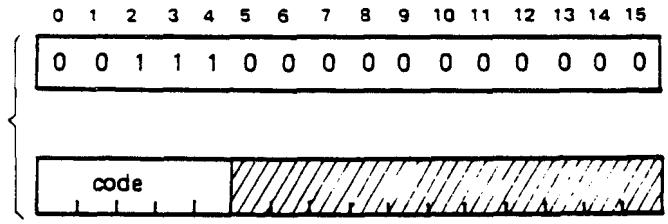

- Adressage indirect post-indexé de mot : l'opérande est le mot mémoire dont l'adresse est donnée par la somme des 16 bits du registre X, et des 15 bits poids faible du relais d'indirection adressé par la base et le déplacement. Dans ce cas, le bit 0 du relais d'indirection vaut 1.

- Adressage direct d'octet : l'opérande est obligatoirement l'octet gauche du mot mémoire adressé par la base et le déplacement. Ce mode d'adressage ne peut être utilisé que dans des cas particuliers.

- Adressage indirect d'octet : l'opérande est obligatoirement l'octet gauche du mot mémoire dont l'adresse est donnée par les 15 bits poids faible du relais d'indirection adressé par la base et le déplacement. Dans ce cas le bit 0 du relais d'indirection vaut 0. Ce mode d'adressage ne donne accès qu'aux octets gauche des mots mémoire dont l'adresse est comprise entre SLO et SLO + 32 767. Ce mode d'adressage ne peut être utilisé que dans des cas particuliers.

- Adressage indirect post-indexé d'octet : dans ce cas le bit 0 du relais d'indirection vaut 1. L'opérande est l'octet gauche du mot mémoire si la valeur du registre X est paire, l'octet droit si la valeur du registre X est impaire. L'adresse du mot est donnée par la somme du registre X décalé algébriquement à droite d'une position, et des 15 bits poids faible du relais d'indirection adressé par la base et le déplacement. En faisant varier l'index par pas de 1 on peut ainsi avoir accès à des octets rangés successivement en mémoire

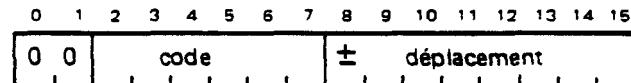

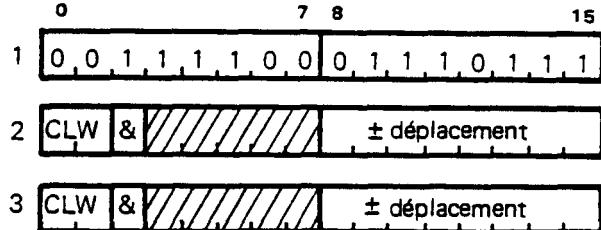

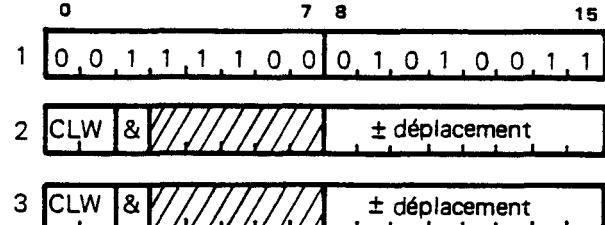

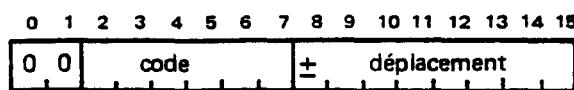

### 3.3 - INSTRUCTIONS DE SAUT

**Bull** Ces instructions utilisent l'adressage par rapport à P ; les bits 8 à 15 comportent un déplacement qui est additionné au registre P pour obtenir l'adresse vers laquelle le saut est effectué. Au moment de l'exécution, P pointe sur l'instruction de saut ; on peut atteindre de cette manière les 128 instructions qui la précédent et les 127 instructions qui la suivent.

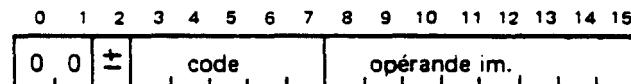

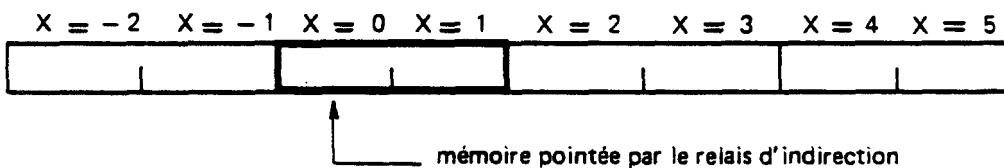

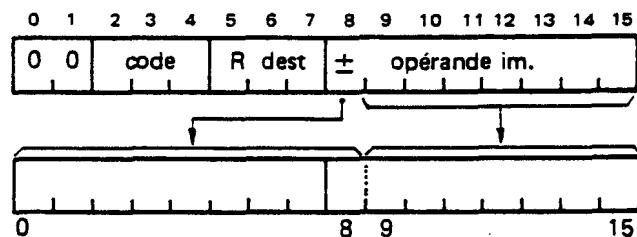

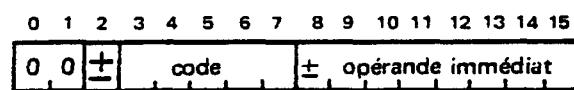

### 3.4 . INSTRUCTIONS AVEC OPÉRANDE IMMÉDIAT 9 BITS

L'opérande effectif comporte 16 bits obtenus de la manière suivante :

les 8 bits poids fort sont identiques au bit 2 de l'instruction, les 8 bits poids faible aux bits 8 - 15 de l'instruction

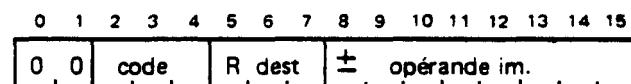

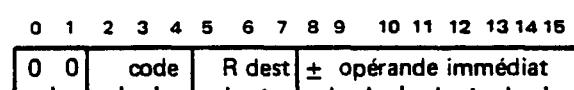

### 3.5 - INSTRUCTION AVEC OPERANDE IMMEDIAT 8 BITS

L'opérande effectif comporte 16 bits obtenus de la manière suivante :

les 9 bits poids fort sont identiques au bit 8 de l'instruction, les 7 bits poids faible aux bits 9 - 15 de l'instruction.

Le codage du registre concerné est celui utilisé dans les instructions registre-registre.

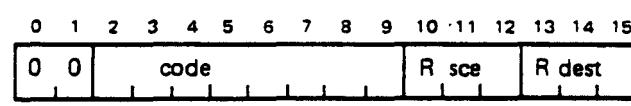

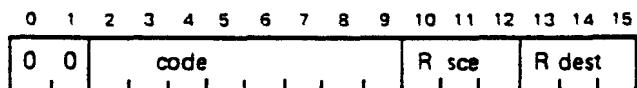

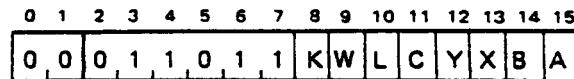

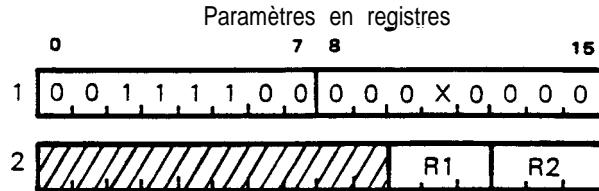

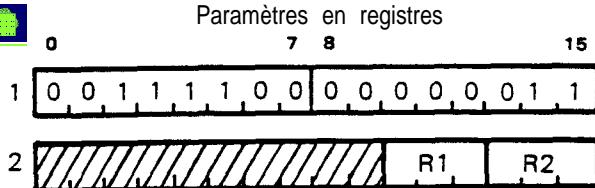

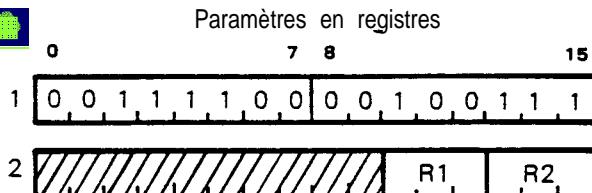

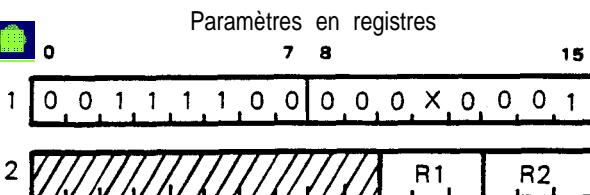

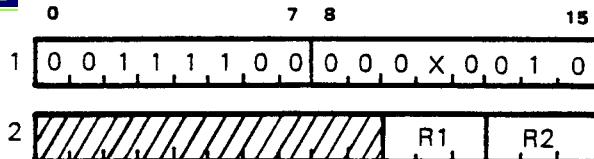

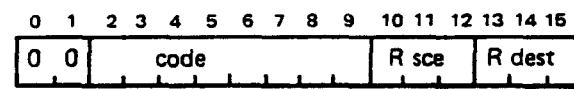

### 3.6 • INSTRUCTIONS REGISTRE-REGISTRE

Le codage du registre source et du registre destination est le suivant :

| A   | B   | X   | Y   | C   | L   | W   | K   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

Pour certaines instructions, le registre source ou le registre destination est implicite ; dans ce cas le contenu des bits correspondants de l'instruction est sans signification.

L'opération est effectuée entre les contenus du registre source et du registre destination et le résultat rangé dans le registre destination.

Il est toujours possible de spécifier le même registre comme registre source et destination.

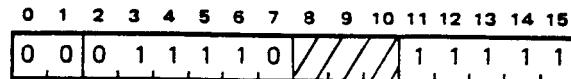

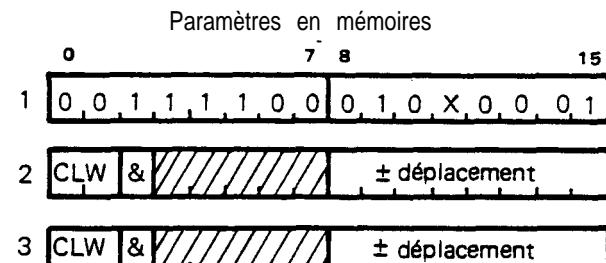

### 3.7 - DÉCALAGES ET OPERATIONS SUR BITS

Les 5 bits poids faible de l'instruction indiquent un nombre de pas de décalage, ou un numéro de bit (de 0 pour A0 à 31 pour B<sub>15</sub>).

Lorsque l'instruction est indexée (bit 10 = 1) les 5 bits poids faible de l'instruction sont additionnés au registre X pour donner sur 5 bits le nombre de pas ou le n° de bit effectif. Cette opération s'effectue modulo 32.

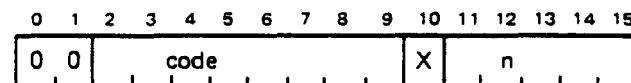

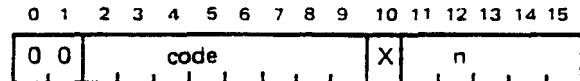

## 3.8 - EXTENSIONS

### 3.8.1 - GENERALITES

Ce format correspond à des codes ouverts pour des instructions optionnelles (flottant simple, double précision, VSS 16, CDA) ou des instructions spécifiques qui peuvent être soit programmées, soit microprogrammées.

En l'absence du microprogramme et/ou du matériel associé(s) à ces instructions, l'unité centrale simule une instruction SVC de rang 0 à 7 selon le paramètre de cette instruction (voir description détaillée chapitre 4).

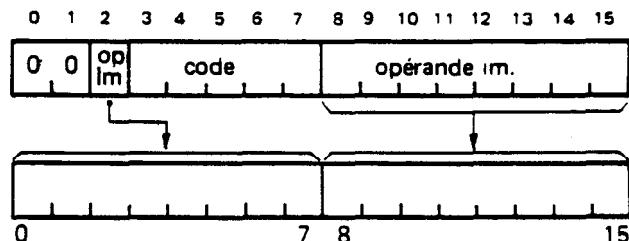

En général les instructions extensions sont codées sur deux mots :

- le premier mot détermine :

- . la famille par le paramètre n sur les bits 5 à 7,

- . éventuellement une sous-famille ou une instruction déterminée sur les bits 8 à 15,

- le deuxième détermine :

- . l'opérande suivant l'un des formats standard (en particulier le format référence mémoire),

- . éventuellement le code de l'instruction comme dans un format standard.

On se référera aux manuels spécifiques pour le codage et la description de ces instructions. En particulier les familles :

- flottant simple (FFP 16),

- CDA,

sont décrites dans ce manuel.

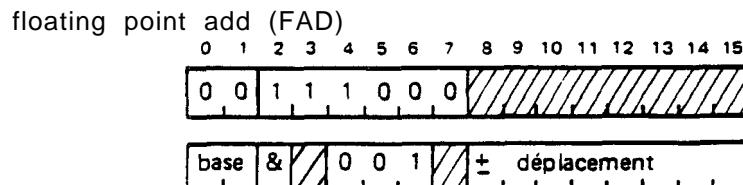

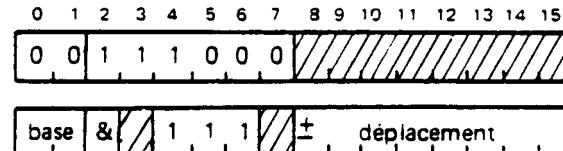

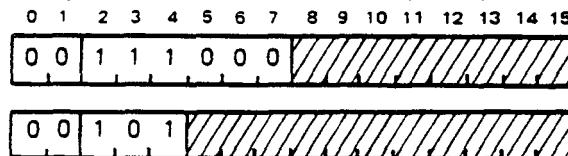

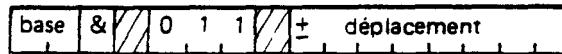

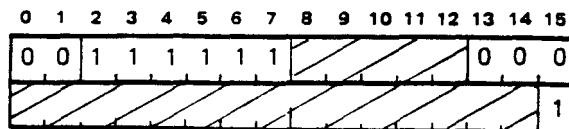

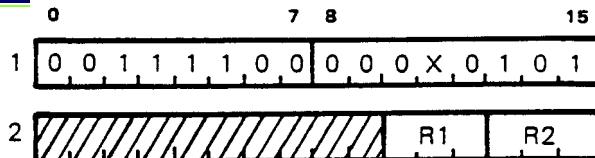

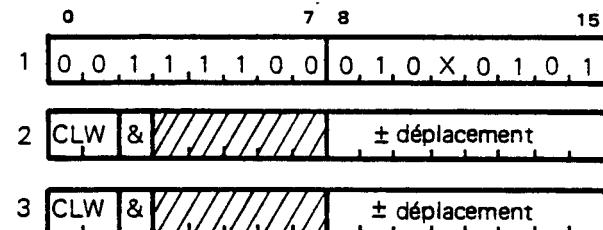

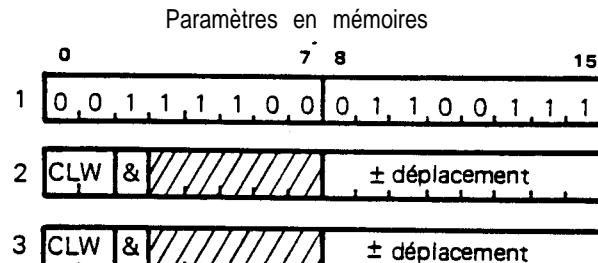

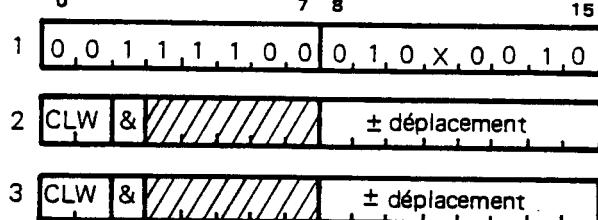

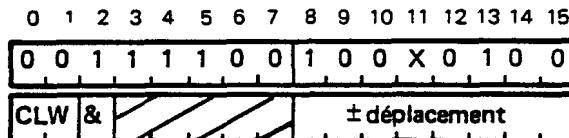

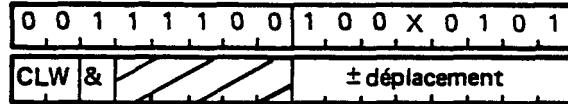

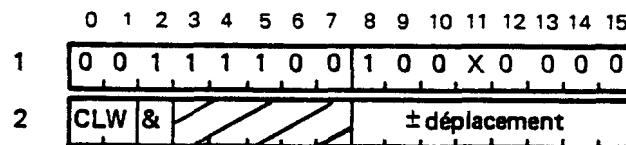

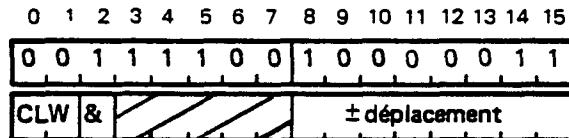

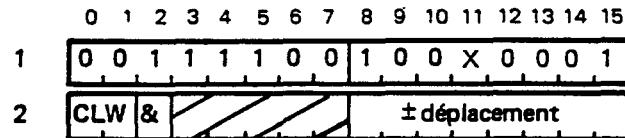

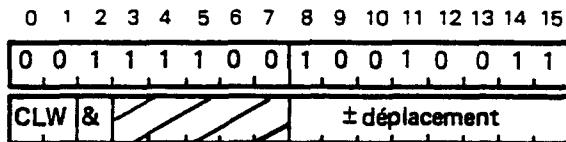

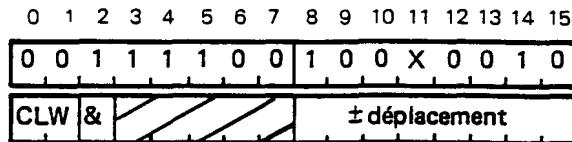

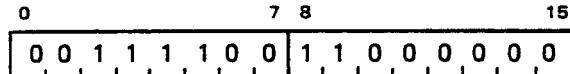

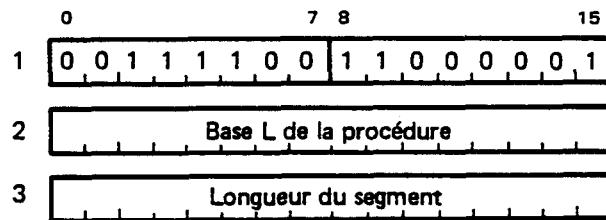

### 3.8.2 - VIRGULE FLOTTANTE SIMPLE PRECISION

Le premier mot est identique pour toutes les instructions en virgule flottante; il comporte le code '3800 et sert à distinguer des autres instructions (voir codes réservés aux extensions § 4). S'il s'agit d'une instruction avec opérande en mémoire les bits 0 et 1 du second mot comportent l'indication de la base. le bit 2 indique l'adressage indirect, les bits 3 à 7 comportent le code opération et les bits 8 à 15 un déplacement.

S'il s'agit d'une instruction dont le ou les opérandes sont dans des registres, le second mot ne comporte que le code opération.

En l'absence de l'opérateur câblé, les instructions FLD, FST, FABS, FNEG, FIX, FCAZ, FCMZ sont exécutées en standard par microprogramme sur certains modèles d'unité centrale **(40 et 65)** ...

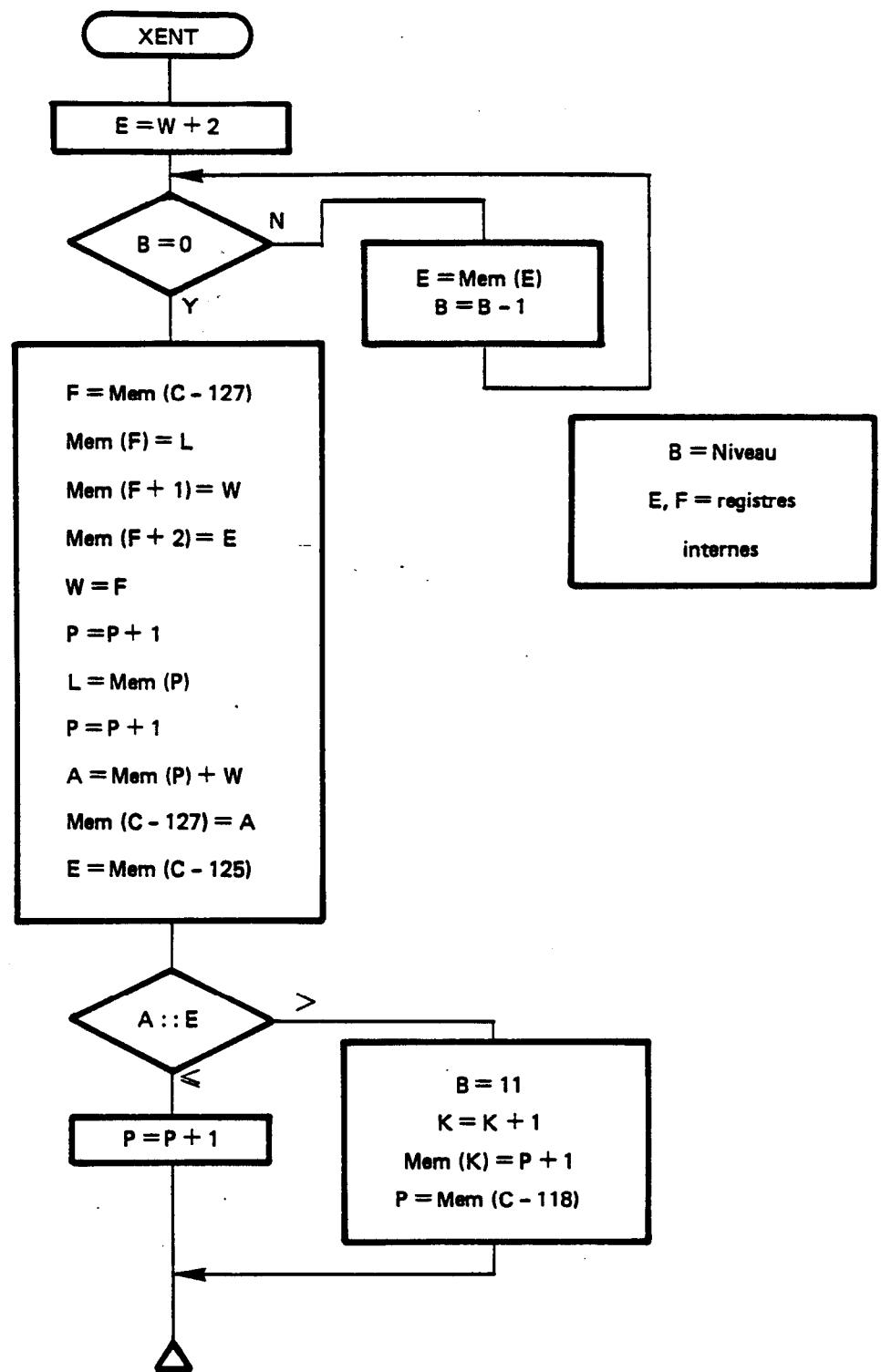

Selon l'option choisie ces instructions sont soit exécutées directement par le calculateur (option flottant hardware) soit exécutées par un ensemble de sous-programmes appelés par le calculateur lorsqu'il rencontre une instruction virgule flottante (option flottant programmé).

L'ensemble des sous-programmes occupe environ 500 mots de mémoire.

Les routines sont réentranttes, de telle manière qu'une tâche effectuant des calculs en virgule flottante puisse être interrompue par une autre tâche effectuant elle aussi des calculs en virgule flottante.

Il n'y a donc pas à modifier les programmes lorsqu'on utilise l'une ou l'autre option. Cependant avec l'option flottant programmé on doit s'assurer que la pile pointée par le registre K comporte suffisamment de mots mémoire (23 mots) pour permettre le déroulement des sous-programmes.

Les opérations sont faites d'une manière interne sur 32 bits pour l'option programmée et sur 27 bits (addition-soustraction) ou 48 bits (multiplication division) pour l'option câblée. Comme il est tenu compte de l'arrondi sur ces bits supplémentaires pour le résultat des opérations arithmétiques il peut y avoir une différence non significative, parce qu'inférieure à la précision des calculs, entre les résultats obtenus avec l'une et l'autre option.

## 4.1 - DESCRIPTION DES INSTRUCTIONS STANDARD

Dans les pages suivantes on trouvera la description de l'ensemble des instructions SOLAR 16.

L'existence ou le fonctionnement de certaines instructions peut dépendre de la présence de certaines "options".

Type de SOLAR 16

| Options   | 04/05 | 30 | 35 | 40 | 65 | 70 | 75 |

|-----------|-------|----|----|----|----|----|----|

| DRPS      | 0     | 1  | 1  | X  | 1  | 1  | 1  |

| Scheduler | X     | 1  | 1  | X  | 1  | 1  | 1  |

| FFP16     | 0     | X  | X  | X  | X  | X  | X  |

| DAP16     | 0     | X  | X  | X  | X  | X  | X  |

| VSS16     | 0     | 0  | 0  | 0  | X  | X  | X  |

| FFM16     | 0     | 0  | 0  | 0  | X  | 1  | X  |

| CDA16     | 0     | 0  | ?  | 0  | 1  | 1  | 1  |

| ISP16     | 0     | 0  | ?  | 0  | 0  | 1  | 0  |

0 - inexistant

1 - standard

X - optionnel

? - voir remarques

Remarques :

Sur SOLAR 16-35 les instructions RCDA et WCDA sont disponibles en standard. Les autres instructions de l'option CDA sont inexistantes.

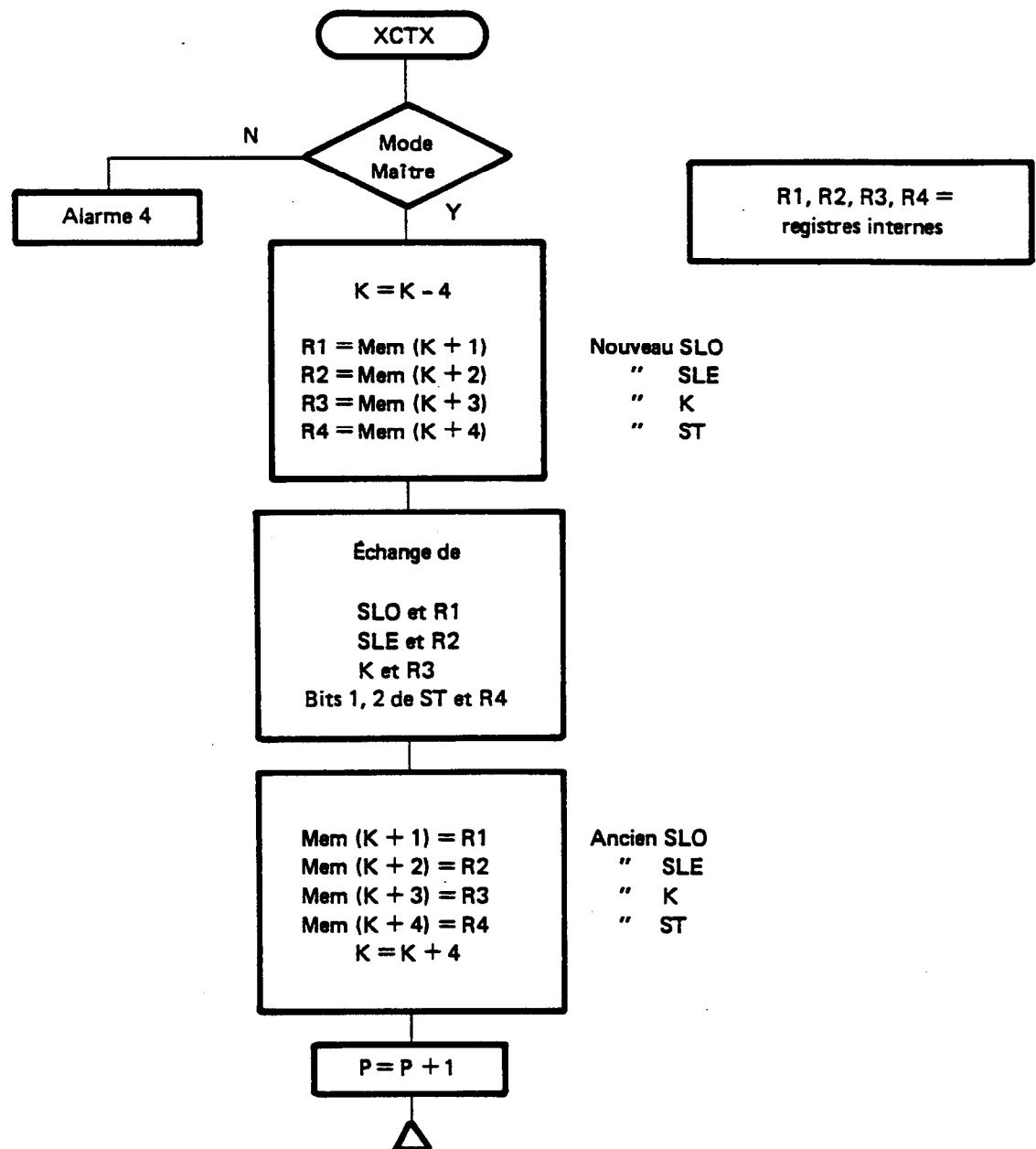

Sur SOLAR 16-35 les instructions de l'option ISP16 sont disponibles en standard à l'exception de l'instruction XCTX.

Les instructions des options DAP16, VSS16 et FFM16 sont décrites dans les notices correspondantes à ces modules.

Les instructions de l'option ISP16 sont décrites dans le chapitre des instructions spéciales (par. 4.2).

Toutes les instructions privilégiées exécutables en mode maître sont aussi exécutables en mode privilégié sur SOLAR 16-70, sauf l'instruction XCTX.

Pour ce qui est du mécanisme DRPS, le mode privilégié est assimilable au mode esclave (MS = 0, SVCS = 0) dans le fonctionnement des instructions sur pile K.

acknowledge (ACK)

Bull

code : 1 E 0 D

Opération effectuée : permet à la tâche qui exécute cette instruction de reconnaître le sous-niveau le plus prioritaire en attente :

- l'indicateur V est mis à 1 si un sous-niveau de type normal est en attente,

- l'indicateur C est mis à 1 si seuls des sous-niveaux de type exception sont en attente,

- le numéro du plus prioritaire des sous-niveaux en attente est chargé dans le registre X :

- . 0 à 15 pour un sous-niveau normal

- . 0 à 47 pour un sous-niveau exception.

Lorsqu'il n'y a pas d'interruption en attente :

- l'indicateur V est positionné à 0

- l'indicateur C est positionné à 0

- le registre X n'est pas modifié.

Dans une tâche différée cette instruction a comme seul effet de remettre à 0 les indicateurs V et C.

Sont modifiés : X, ST

| Indicateurs | : | V | C |                       |

|-------------|---|---|---|-----------------------|

|             |   | 0 | 0 | pas de sous-niveau    |

|             |   | 1 | 0 | sous-niveau normal    |

|             |   | 0 | 1 | sous-niveau exception |

Alarmas possibles : - protection mémoire **05**

- mémoire inexistante **05**

- parité

ATTENTION : ACK ne doit pas être utilisée dans la tache alarme, ni dans la tâche défaut secteur.

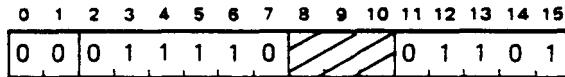

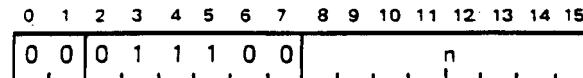

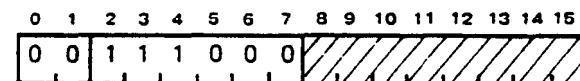

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |   |   |    |    | 0  | 0  | 0  | 0  |

Mode : maître

Code : 1 E 0 0

Opération effectuée : L'instruction ACQ annule la tâche immédiate en cours en remettant à zéro le bit du registre HV correspondant à cette tâche et provoque le lancement de la tâche interruption ou de la tâche différée la plus prioritaire en attente.

Les masques IOM et IPM sont mis à zéro.

La commutation de tâche se fait par un changement de contexte partiel (C, K, P, S) qui sauvegarde le contexte de la tâche abandonnée et restitue le contexte de la tâche reprise.

ACQ peut être aussi utilisée dans une tâche différée (dans ce cas le registre HV n'est pas modifié) pour provoquer un changement de contexte après modification par programme des files ASTF, ESTF et RSTF (mais surtout pas de NS I).

En l'absence de l'option scheduler, cette instruction ne doit pas être utilisée dans une tâche différée.

Sont modifiés : - la PST de la tâche exécutant l'ACQ,

- le contexte partiel C, K, P, S (ACQ dans une tâche hardware)

- le contexte complet (ACQ dans une tâche différée)

- HV, ST.

Indicateurs : ceux du nouveau contexte, IOM, IPM

Alarmes possibles : - protection mémoire **05**

- mémoire inexistante **03**

- parité

- instruction privilégiée

Option : scheduler

Mode : maître

| Code   | Direct | Indirect |

|--------|--------|----------|

| base C | 5C--   | 7C--     |

| base L | 9C--   | BC--     |

| base W | DC--   | FC--     |

Adressage : mémoire (1er mot du sémaphore)

Opération effectuée : la seule différence entre l'opération effectuée par ACT sur un sémaphore de synchronisation (bit 0 du premier mot du sémaphore à zéro) et sur un sémaphore d'appel (bit 0 du premier mot du sémaphore à un) est le traitement de la file paramètre :

**dans le cas d'un sémaphore d'appel, le bit de la file paramètre dont le rang ( $\geq 0$  et  $\leq 32\ 767$ ) est égal à la valeur du registre Y est mis à 1.** Ensuite, dans les deux cas le compteur du sémaphore est augmenté de 1 :

- si après cette modification le compteur a une valeur positive la tâche qui effectue l'instruction ACT se poursuit ;

- si après cette modification le compteur à une valeur nulle ou négative :

- le bit de la file ESTF dont le rang est égal au n° de la tâche en attente sur le sémaphore est mis à 1 (la tâche est démasquée),

- si la tâche qui effectue l'instruction ACT est plus prioritaire elle se poursuit normalement, sinon le scheduler effectue un changement de contexte au profit de la tâche démasquée.

Les indicateurs IOM, IPM sont remis à 0 (avant passage éventuel dans le scheduler).

■ merviennent : le sémaphore adressé

NS

Sont modifiés : le sémaphore adressé

NS et tous les registres s'il y a changement de contexte

ST

Indicateurs : IOM, IPM, plus le changement de contexte éventuel

Alarmes possibles : - protection mémoire 05

- mémoire inexistante 05

- parité

- instruction privilégiée

- instruction optionnelle inexistante

ATTENTION : le rang du bit mis à 1 dans la file paramètre d'un sémaphore d'appel n'est pas égal au n° de la tâche qui effectue l'instruction ACT, mais au contenu du registre Y, et peut avoir une valeur supérieure à 128.

activate debug (ACTD)

Bull

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |   |   |    | 0  | 0  | 1  | 0  | 1  |

Code : 1 E 0 5

Opération effectuée : permet de déclencher l'alarme numéro 9. Cette alarme provoque le lancement de la tâche immédiate. 0 comme toutes les alarmes.

On peut ainsi appeler un programme de mise au point (AID par exemple).

Sont modifiés : les registres du contexte partiel (C, K, P, S)

Indicateurs : ceux du nouveau contexte

Alarmes possibles : - protection mémoire

- mémoire inexistante

- parité

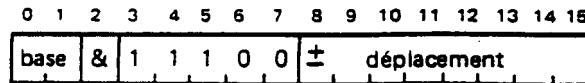

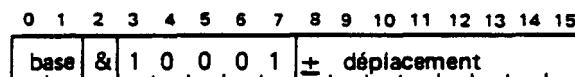

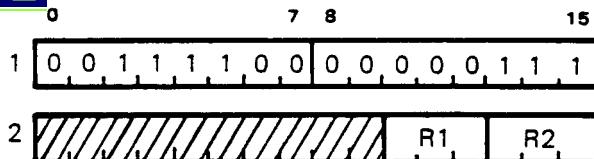

add (AD)

**AD**

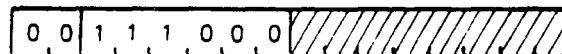

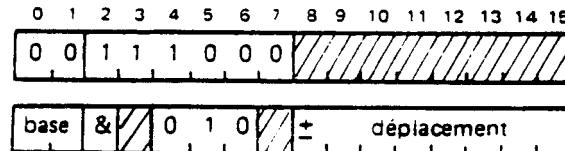

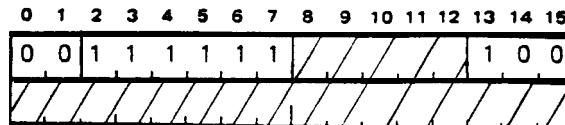

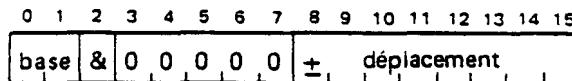

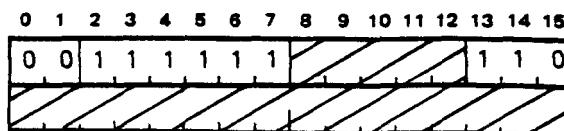

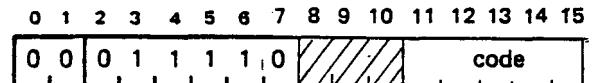

| 0    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9           | 10 | 11 | 12 | 13 | 14 | 15 |

|------|---|---|---|---|---|---|---|---|-------------|----|----|----|----|----|----|

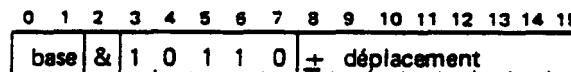

| base | & | 0 | 1 | 0 | 0 | 1 |   | ± | déplacement |    |    |    |    |    |    |

| Code : | direct | indirect |

|--------|--------|----------|

| base C | 49     | 69       |

| base L | 89     | A9       |

| base W | C9     | E9       |

Adressage : mémoire (mot)

Opération effectuée : le contenu du mot mémoire adressé est additionné au registre A.

Les indicateurs V et C sont positionnés de la manière indiquée aux § 1.1 et 1.2

Interviennent : . le mot mémoire adressé

. A

Sont modifiés : . A

. ST

Indicateurs : V : débordement addition

C : report addition

Alarmes possibles : - protection mémoire

- mémoire inexistante

- parité

Bull

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14    | 15 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|-------|----|

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | /  | /  | /  | /  | Rdest |    |

Code : 2D8\_

Adressage : registre - registre

Opérations effectuée : la valeur de l'indicateur C est additionnée au registre destination.

Les Indicateurs V et C sont positionnés de la manière indiquée aux § 1.1 et 1.2. On peut ainsi effectuer des additions en double longueur, le report de l'addition des poids faibles étant additionné aux poids forts.

Intervient : un des registres A B X Y C

LWK

Sont modifiés : . un des registres A B X Y C

LWK.

. ST

Indicateurs : V : débordement addition

C : report addition

Alarms possibles : - protection mémoire

- mémoire inexistante

- parité

add registers (ADR)

Bull

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10   | 11 | 12    | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|------|----|-------|----|----|----|

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | Rsce |    | Rdest |    |    |    |

Code : 2C0\_

Adressage : registre - registre

Opération effectuée : le contenu du registre source est additionné au registre destination.

Les indicateurs C et V sont positionnés de la manière indiquée aux § 1.1 et 1.2. On peut ainsi :

- additionner un quelconque des huit registres A B X Y C L W K à un autre de ces registres,

- doubler le contenu d'un de ces registres en précisant le même registre comme source et destination.

Interviennent : deux des registres A B X Y C

LWK.

Sont modifiés : • un des registres A B X Y C

LWK

• ST

Indicateurs : V : débordement addition

C : rapport addition

Alarms possibles : - protection mémoire

- mémoire inexistante

- parité

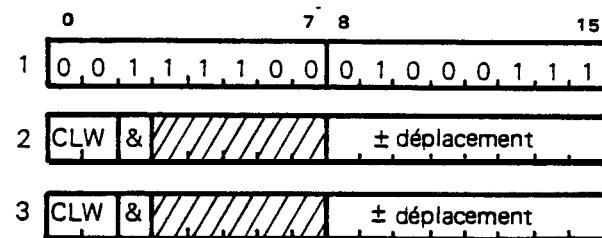

## add register immediate (ADRI)

**ADRI**

Bull

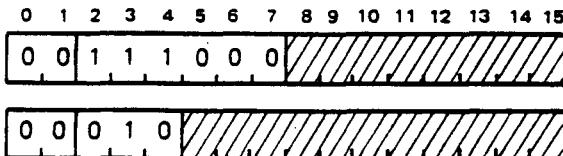

| 0 | 1 | 2 | 3 | 4 | 5      | 6 | 7           | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---|---|---|---|---|--------|---|-------------|---|---|----|----|----|----|----|----|

| 0 | 0 | 0 | 0 | 1 | R dest | ± | opérande im |   |   |    |    |    |    |    |    |

|        |     |        |

|--------|-----|--------|

| Code : | 08_ | pour A |

|        | 09_ | pour B |

|        | 0A_ | pour X |

|        | 0B_ | pour Y |

|        | 0C_ | pour C |

|        | 0D_ | pour L |

|        | 0E_ | pour W |

|        | 0F_ | pour K |

Opération effectuée : la valeur de l'opérande immédiat est additionnée au registre destination.

L'opérande immédiat est étendu sur 16 bits, ses 9 bits poids fort étant identiques au bit 8 de l'instruction, ses 7 bits poids faible étant identiques aux bits 9 à 15 de l'instruction. Les indicateurs C et V sont positionnés de la manière indiquée aux § 1.1 et 1.2. On peut ainsi additionner à l'un des huit registres A B X Y C L W K une valeur comprise entre - 128 et + 127

|               |                                                                                   |

|---------------|-----------------------------------------------------------------------------------|

| Interviennent | : . l'opérande immédiat (sur 16 bits)<br>. le registre précisé dans l'instruction |

| Sont modifiés | : . le registre précisé dans l'instruction<br>. ST                                |

| Indicateurs   | : . V débordement addition<br>. C report addition                                 |

Alarmas possibles : - protection mémoire

- mémoire inexisteante

- parité

ATTENTION : cette instruction est la seule qui utilise un opérande immédiat sur 8 bits (compris entre + 127 et - 128).

## add register to P (ADRP)

**ADRP**

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10    | 11 | 12 | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|-------|----|----|----|----|----|

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | Rscpe |    |    |    |    |    |

Code : **2 F 8 \_**

Adressage : registre - registre

Opération effectuée : le contenu du registre source est additionné au registre P (qui contient l'adresse de l'instruction ADRP elle-même).

On peut ainsi :

- réaliser un aiguillage en fonction d'un indice

- remplacer l'instruction BR dans des programmes translatables.

Interviennent : un des registres A B X Y C L W K P

Est modifié : P

Indicateurs : non modifiés

Alarmas possibles : - protection mémoire

- mémoire inexisteante

- parité

ATTENTION : la valeur de P additionnée est l'adresse de l'instruction ADRP elle-même.

Bull

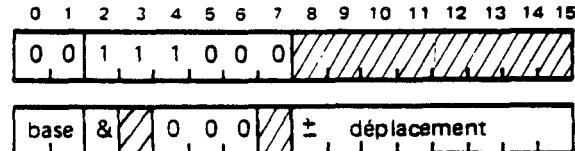

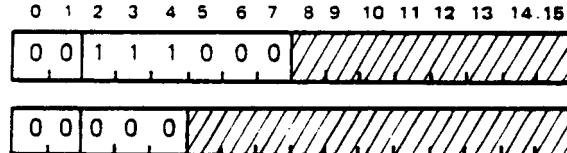

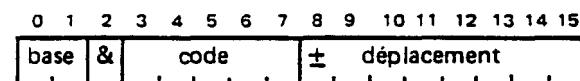

| 0    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9           | 10 | 11 | 12 | 13 | 14 | 15 |

|------|---|---|---|---|---|---|---|---|-------------|----|----|----|----|----|----|

| base | & | 1 | 0 | 0 | 1 | 1 |   | ± | déplacement |    |    |    |    |    |    |

| Code   | direct | indirect |

|--------|--------|----------|

| base C | 53--   | 73--     |

| base L | 93--   | B3--     |

| base W | D3--   | F3--     |

Adressage : mémoire (mot)

Opération effectuée : le résultat de l'intersection logique des 16 bits du registre A et du mot mémoire adressé est rangé dans le registre A.

(Intersection : l'intersection de 1 et 1 vaut 1, les intersections de 1 et 0, 0 et 1, 0 et 0 valent 0).

Interviennent : . le mot mémoire adressé

. A

Est modifié : A

Indicateurs : non modifiés

Alarmes possibles : - protection mémoire

- mémoire inexisteante

- parité

05

05

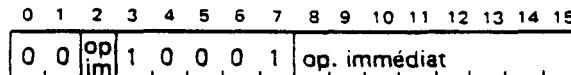

and immediate (ANDI)

**ANDI**

| 0 | 1 | 2        | 3 | 4 | 5 | 6 | 7 | 8            | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

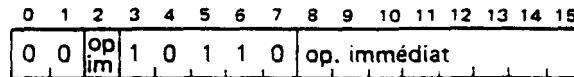

|---|---|----------|---|---|---|---|---|--------------|---|----|----|----|----|----|----|

| 0 | 0 | op<br>im | 1 | 0 | 0 | 1 | 1 | op. immédiat |   |    |    |    |    |    |    |

| Code | bit 2 = 0 | 13-- |

|------|-----------|------|

|      | bit 2 = 1 | 33-- |

Adressage : immédiat (9 bits)

Opération effectuée : le résultat de l'intersection des 16 bits du registre A et de l'opérande immédiat est rangé dans le registre A. L'opérande immédiat est étendu sur 16 bits, ses huit bits poids fort étant identiques au bit 2 de l'instruction, ses huit bits poids faible étant identiques aux bits 8 à 15 de l'instruction.

On peut ainsi effectuer une intersection entre A et un opérande immédiat compris entre '0000 et '00FF ou entre 'FF00 et 'FFFF.

Interviennent : . l'opérande immédiat (sur 16 bits)

. A

Est modifié : A

Indicateurs : non modifiés

Alarmes possibles : -protection mémoire

-mémoire inexisteante

-parité

05

05

and registers (ANDR)

Bull

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10  | 11 | 12    | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|-----|----|-------|----|----|----|

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | Rsc |    | Rdest |    |    |    |

Code : 2D9\_

Adressage : registre • registre

Opération effectuée : le résultat de l'intersection logique des 16 bits du registre source et du registre destination est rangé dans le registre destination.

On peut ainsi faire l'intersection logique de deux quelconques des huit registres A B X Y C L W K.

Interviennent : deux des registres A B X Y C L W K.

Est modifié : un des registres A B X Y C L W K.

Indicateurs : non modifiés

Alarms possibles : - protection mémoire

- mémoire inexiste

- parité

05

05

arm (ARM)

**ARM**

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9           | 10 | 11 | 12 | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|-------------|----|----|----|----|----|----|

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | X |   | nº de tâche |    |    |    |    |    |    |

Option : scheduler

Mode : maître

Code : 1 F \_ \_

Adressage : indexation possible

Opération effectuée : le bit de la file ASTF correspondant au numéro de la tâche indiqué par l'instruction est mis à 1. Si l'instruction n'est pas indexée le numéro de la tâche armée est contenu dans les bits 9 à 15 de l'instruction. Si l'instruction est indexée ce numéro est la somme des bits 9 à 15 de l'instruction et des 16 bits du registre X. Les masques IOM et IPM sont remis à zéro.

Lorsque ARM est rencontré dans une tâche immédiate cette tâche immédiate se poursuit.

Lorsqu'une tâche différée arme une tâche différée plus prioritaire, le scheduler provoque un changement de contexte pour lancer la tâche différée qui vient d'être armée.

Intervient : le nº de tâche indiqué dans l'instruction

Sont modifiés : - la file ASTF

- NS et tous les registres s'il y a changement de contexte

- S T

Indicateurs : IOM, IPM, plus le changement de contexte éventuel

Alarmes possibles :

- protection mémoire

- mémoire inexiste

- parité

- instruction privilégiée

- instruction optionnelle inexiste

05

05

ATTENTION : lorsqu'il y a indexation, le numéro de tâche est pris modulo 128

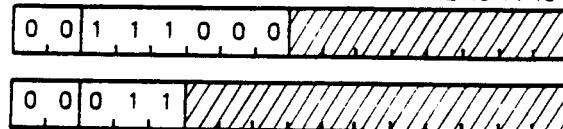

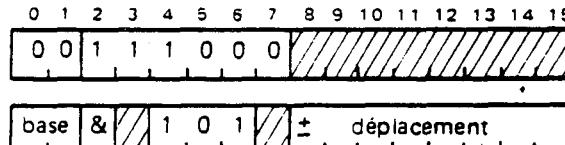

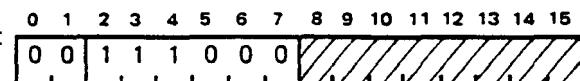

| 0    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8           | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|------|---|---|---|---|---|---|---|-------------|---|----|----|----|----|----|----|

| base | & | 0 | 0 | 1 | 0 | 1 | ± | déplacement |   |    |    |    |    |    |    |

| Code   | : | direct | indirect |

|--------|---|--------|----------|

| base C |   | 45__   | 65__     |

| base L |   | 85__   | A5__     |

| base W |   | C5__   | E5__     |

**Adressage** : mémoire (mot)

Opération effectuée : le contenu du mot mémoire adressé est chargé dans le registre P.

On peut ainsi en chargeant dans P un mot mémoire qui contient l'adresse vers laquelle le branch est effectué avoir accès à des instructions qu'on ne peut pas atteindre par JMP.

Intervient : le mot mémoire adressé

Est modifié : P

Indicateurs : non modifiés

Alarmes possibles : - protection mémoire

- mémoire inexistante

- parité

**ATTENTION** : une instruction BR indirecte fait intervenir deux constantes adresse : la première (éventuellement indexée) fournit l'adresse de la seconde qui est chargée dans P.

### branch subroutine (BSR)

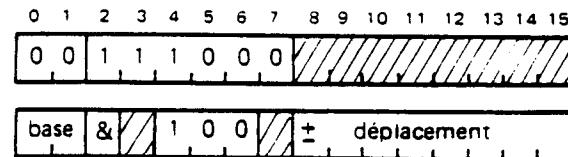

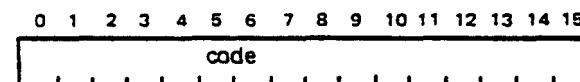

| 0    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8           | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|------|---|---|---|---|---|---|---|-------------|---|----|----|----|----|----|----|

| base | & | 0 | 0 | 1 | 1 | 0 | ± | déplacement |   |    |    |    |    |    |    |

| Code   | : | direct | indirect |

|--------|---|--------|----------|

| base C |   | 46__   | 66__     |

| base L |   | 86__   | A6__     |

| base W |   | C6__   | E6__     |

**Adressage** : mémoire (mot)

Opération effectuée : le contenu du registre K est augmenté de 1, puis l'adresse de l'instruction qui suit le BSR est rangée dans le mot mémoire pointé par K.

Enfin le registre P est chargé par le contenu du mot mémoire adressé par l'instruction BSR.

On peut ainsi appeler un sous-programme en sauvegardant le point de retour :

- le mot mémoire chargé dans P contient l'adresse du sous-programme appelé

- l'adresse de retour rangée en mémoire sera reprise à la fin du sous-programme par une instruction RSR (la fonction de RSR est complémentaire de celle de BSR).

- les appels imbriqués de sous-programmes sont possibles grâce à l'addition de 1 au registre K effectuée par l'instruction BSR, cette évolution de K pour la sauvegarde de l'adresse de retour étant de plus homogène avec l'évolution de K pour les sauvegardes effectuées par SVC et PSR.

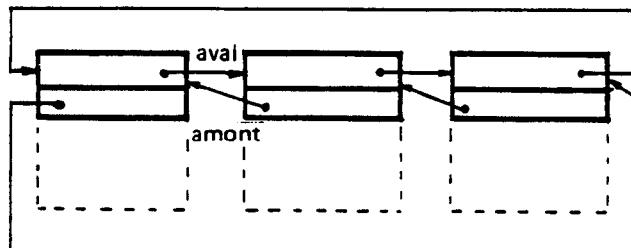

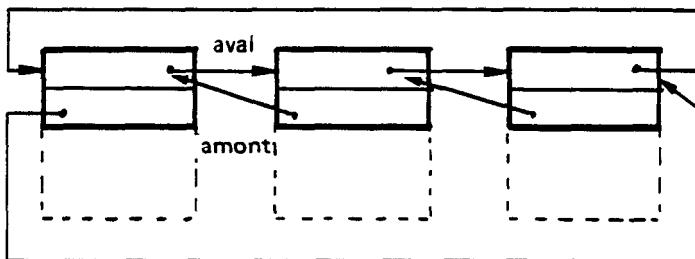

Si l'option DRPS est présente, le fonctionnement est identique mais K contient soit une adresse absolue, soit une adresse relative à SLO selon les indicateurs MS et SVCS :

- si l'instruction est exécutée en mode maître (MS = 1 et SVCS = 0), K contient une adresse absolue.

- si l'instruction est exécutée en mode esclave (MS = 0 et SVCS = 0) ou en mode maître mais dans une requête superviseur (cf SVC) appelée en mode esclave (MS = 1 et SVCS = 1), K contient une adresse relative à SLO.

De plus, si l'instruction est exécutée en mode esclave, l'adresse de retour qui est empilée est également une adresse relative à SLO.

Interviennent : le mot mémoire adressé

K, ST

Sont modifiés : P

K

le mot mémoire pointé par K

Indicateurs : non modifiés

Alarmes possibles : - protection mémoire

- mémoire inexistante

- parité

ATTENTION : - K pointe toujours sur la mémoire occupée de la pile d'adresse la plus grande : ici le dernier point de retour rangé.

- le programme peut passer en mode esclave à la suite d'une alarme.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10   | 11    | 12 | 13 | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|------|-------|----|----|----|----|

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | Rsrc | Rdest |    |    |    |    |

Code : **2 D 4**

Adressage : registre - registre

Opération effectuée : le résultat de l'intersection logique des 16 bits du registre destination et du complément logique du contenu du registre source est rangé dans le registre destination.