# **BIPOLAR DIGITAL ICs**

DATA BOOK 1985/86

THOMSON SEMICONDUCTEURS

# BIPOLAR DIGITAL ICs

| Bipolar memories              |

|-------------------------------|

| Bipolar microprocessor series |

| Semi-custom ICs               |

| Military and Hi-Rel ICs       |

| Quality information           |

| Package dimensions            |

| _ |   |  |

|---|---|--|

|   | 1 |  |

|   | 4 |  |

|   |   |  |

5

| Quality | information |

|---------|-------------|

|---------|-------------|

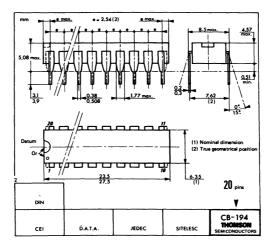

Package dimensions

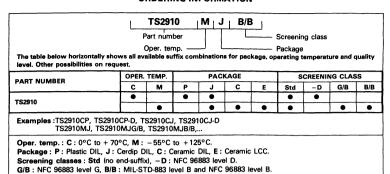

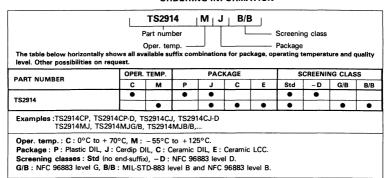

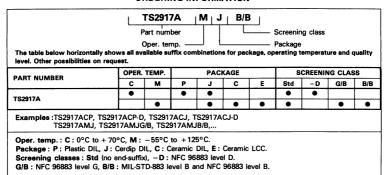

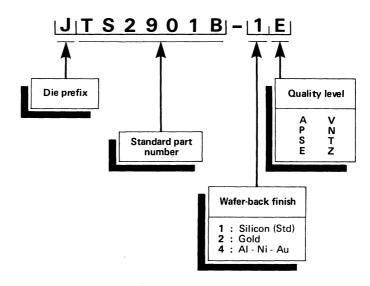

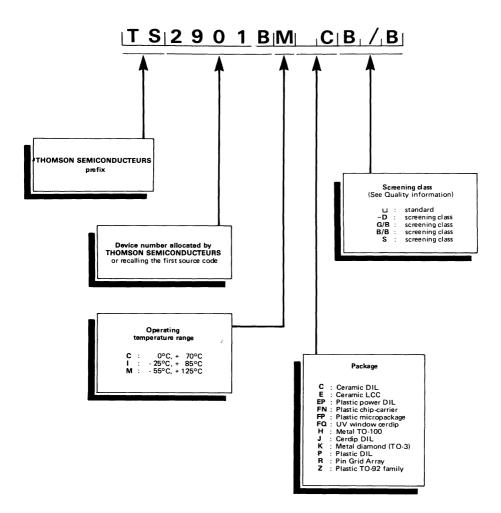

**Ordering information**

Over the last four years, THOMSON SEMICONDUCTEURS has developed a new high performance line of standard Digital Bipolar ICs including advanced PROMs, microprocessors (2900 second source) and gate arrays.

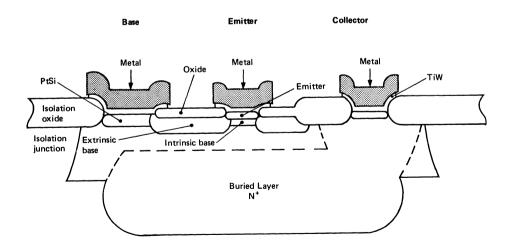

In order to provide first range VLSI functions for high speed applications, THOMSON SEMICON-DUCTEURS uses the necessary technologies such as H-BIP1 (advanced TTL process), H-BIP2 (lateral oxide isolation process) and Triple Diffused (2  $\mu$  - size and wafer stepper),

Concerning the future, THOMSON SEMICONDUCTEURS will carry on its PROM plan (from 8 K up to 128 K) using state-of-the-art H-BIP3 process (full oxide isolation process).

For more information about new products, please contact your local THOMSON SEMICON-DUCTEURS sales representatives and ask for specific technical literature.

The specification of the devices referred to in this data book may have changed. For up dated information regarding static and dynamic characteristics, please consult the current issue of the relevant data sheet.

#### Industrial power: a solid support

Thousands of people trained to our exacting professional standards, the latest state-of-the-art production and control equipment, product design aided by powerful data processing resources - all these made it possible to produce millions of integrated circuits and discrete components in these THOMSON SEMICONDUCTEURS plants last year:

#### In France

- St-Egreve: bipolar integrated circuits, ECL-TTL gate arrays, bipolar custom products.

- military and Hi-Rel integrated circuits covering the whole product spectrum according to international standards.

(MIL-STD-883 C and European standards).

- Grenoble: MOS circuits & microsystems, CMOS, MOS custom products.

- · Rousset: MOS circuits.

- Aix-en-Provence: switching power transistors, rectifiers, zeners.

- Tours: thyristors and triacs, switching power MOS transistors, zeners.

- Alençon: power modules, molding and assembly of semiconductors to perform complex functions, thyristors, triacs, rectifier diodes and zeners.

#### In United States

Montgomeryville, PA: RF and microwave power transistors for mobile communications. TV transmission, radar, IFF, DME, and TACAN applications.

## In Morocco, Brazil, the Philippines and Singapore

· Assembly and test centers.

#### Commercial network: a worlwide service

THOMSON SEMICONDUCTEURS has one of the most comprehensive service and technical networks in the world at its disposal, with comprecial services operating in Germany, Austria, Belgium, Brazil, Canada, Spain, France, Hong Kong, Ireland, Italy, Japan, Morocco, the Netherlands, Singapore, the United Kingdom, and the United States, in addition to its worldwide distribution network.

THOMSON SEMICONDUCTEURS is always at the customer's service, with technical assistance, applications laboratories, software, and development of microcontrollers, gate array networks and custom circuits available to meet their needs.

MOS circuit plant in Grenoble (France)

Bipolar and military & space circuits plants in St-Egreve (France)

# THOMSON SEMICONDUCTEURS created by the THOMSON Group to meet today's most demanding technological changes.

With its four divisions-MOS, Bipolar, Discrete, Military & Space-THOMSON SEMICONDUC-TEURS represents a major commitment to the advancement of electronics. It has enabled the THOMSON Group to implement a whole new set of strategies, technologies, production capabilities, technical and commercial services, and to focus on delivering effective answers to the multiple challenges facing today's electronics industry.

#### Technological competence: a guarantee

THOMSON SEMICONDUCTEURS maintains Research and Development Laboratories in Grenoble, St-Egreve, Tours, Rousset, Aix-en-Provence and Montgomeryville, PA (USA). Together with their Central Laboratories. THOMSON SEMICONDUCTEURS conducts highly independent research, and offers its customers the latest advances in technology:

Research activities dedicated to the development of new and improved products are carried out simultaneously in all these laboratories.

Among the more significant developments:

- Improved MOS and bipolar technologies for linear and digital LSI circuits and power circuits.

- New packaging processes to increase miniaturization and improve reliability; e.g. SO, SOT, plastic and ceramic chip-carriers.

- New power circuit packages: TOP 3, ISOTOP, etc.

- Technologies of the future, notably in solid state physics leading to the development of new components in professional, industrial and consumer electronics, as well as the telecommunications and computer aided design fields.

A full 20% of THOMSON SEMICONDUCTEURS sales revenues are reinsvested in Research and Development.

MOS circuit plant in Rousset (France)

### CONTENTS -

|                                                   | Page |

|---------------------------------------------------|------|

| CHAPTER 1 - BIPOLAR MEMORIES                      | 7    |

| TS71180/TS71181 8 K (1 K×8) bipolar PROMs         | 9    |

| • TS71190/TS71191 16 K (2 K×8) bipolar PROMs      |      |

| <b>TS71321</b> 32 K (4 K×8) bipolar PROMs         | 21   |

| <b>TS71640/TS71641</b> 64 K (8 K×8) bipolar PROMs | 27   |

| CHAPTER 2 - BIPOLAR MICROPROCESSOR SERIES         | 31   |

| ● TS2901B 4-bit microprocessor slice              | 33   |

| ●TS2901C High speed 4-bit microprocessor slice    | 59   |

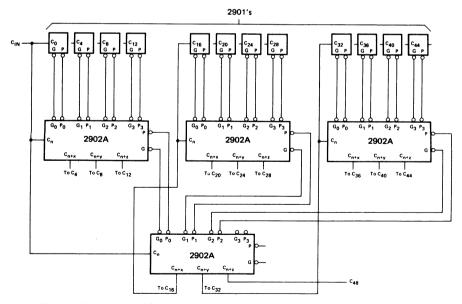

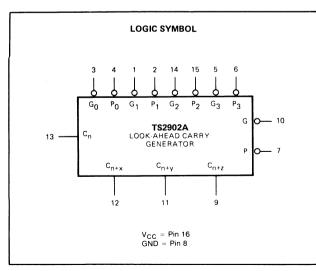

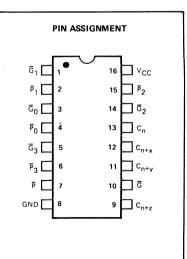

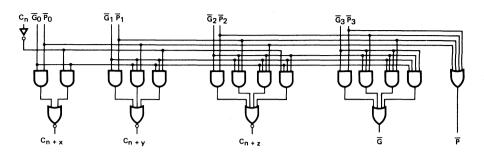

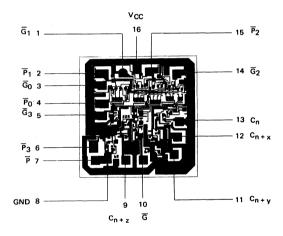

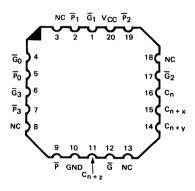

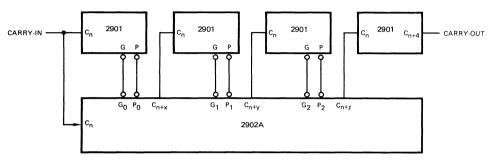

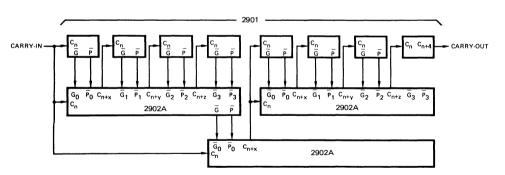

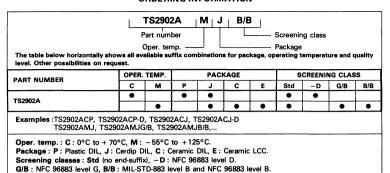

| ●TS2902A High speed look-ahead carry generator    | 83   |

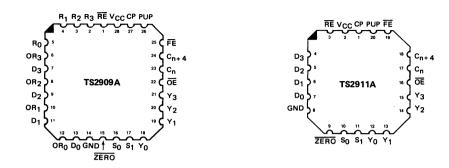

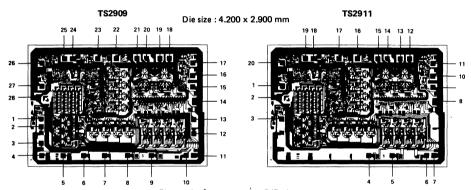

| ●TS2909A 4-bit microprogram sequencer             | 89   |

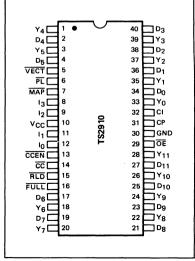

| ●TS2910 12-bit microprogram sequencer             | 105  |

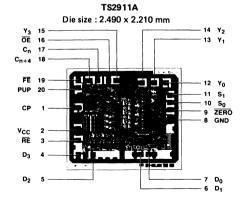

| ●TS2911A 4-bit microprogram sequencer             | 89   |

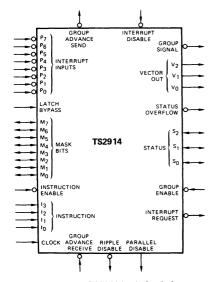

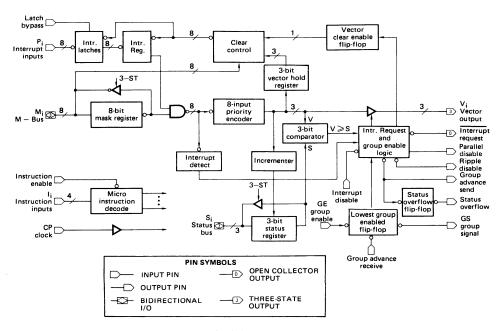

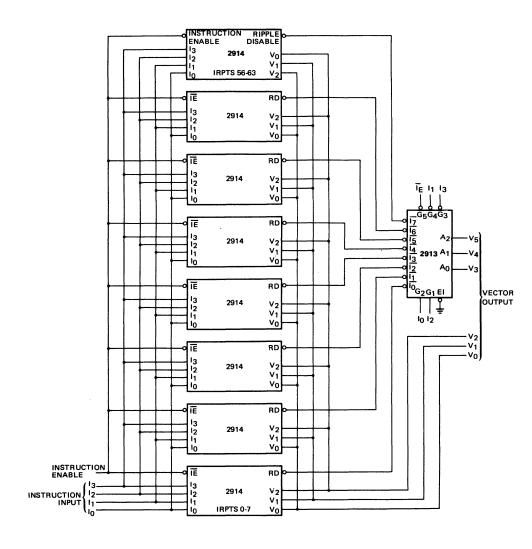

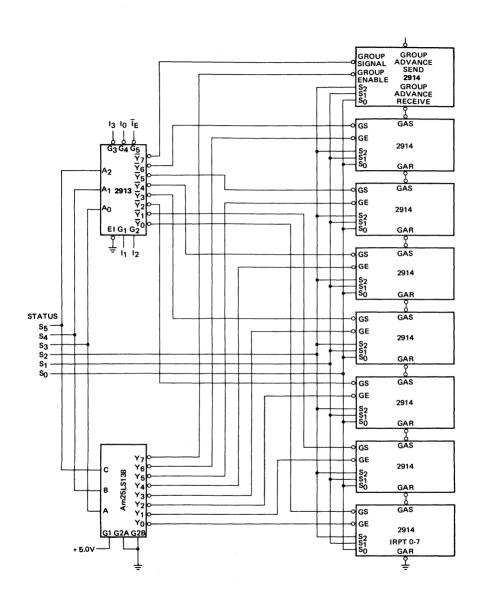

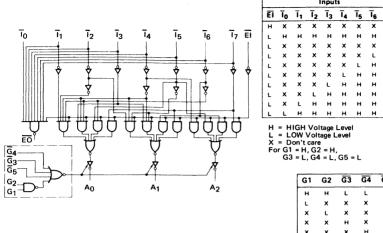

| ●TS2914 Vectored priority interrupt controller    |      |

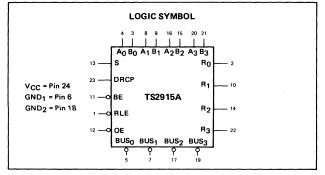

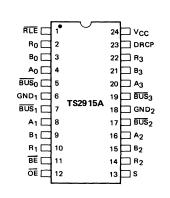

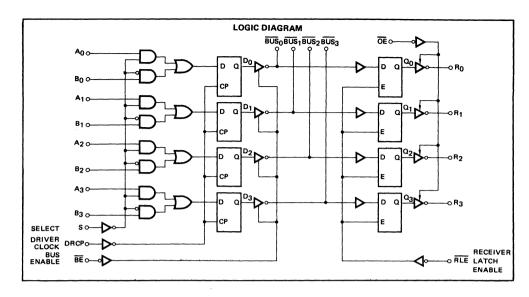

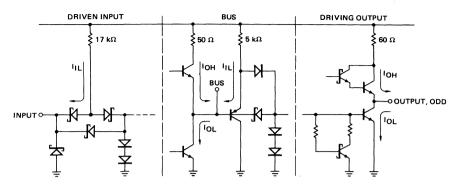

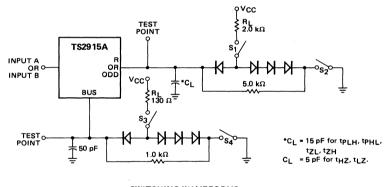

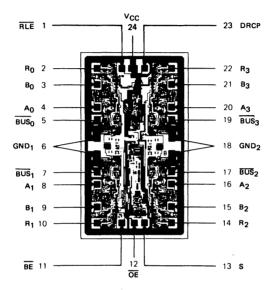

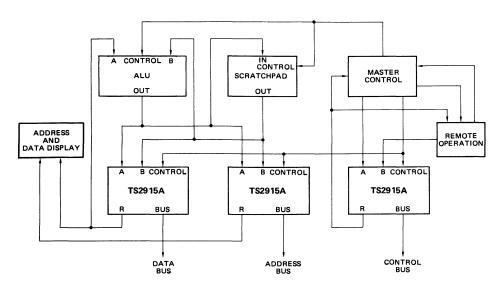

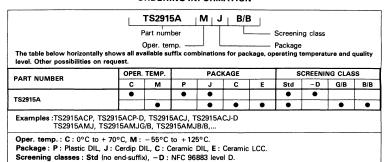

| ●TS2915A Quad three-state bus transceiver         | 147  |

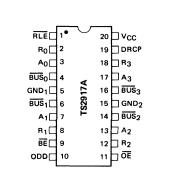

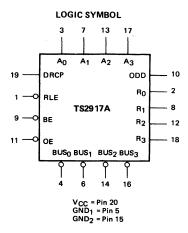

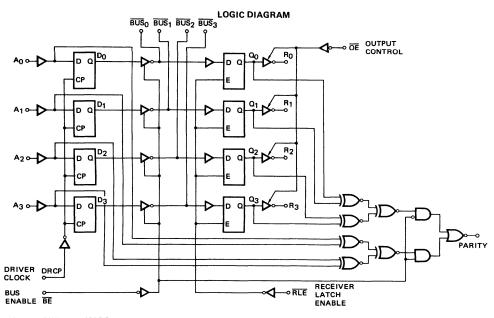

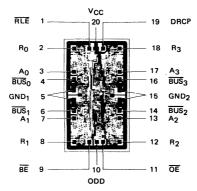

| ●TS2917A Quad data bus transceiver                |      |

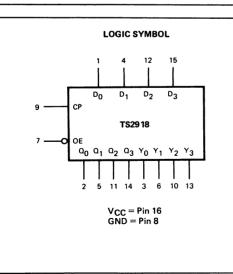

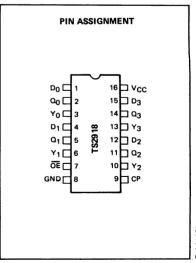

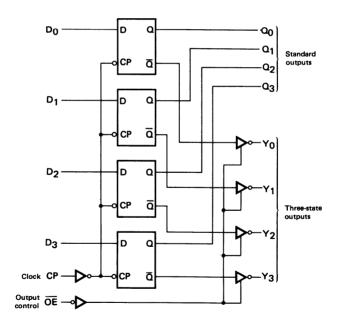

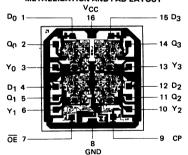

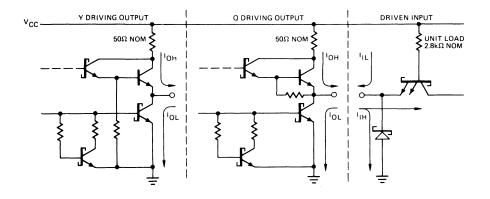

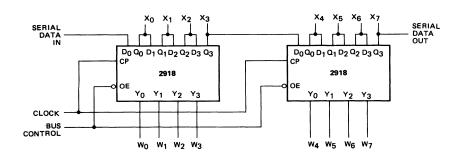

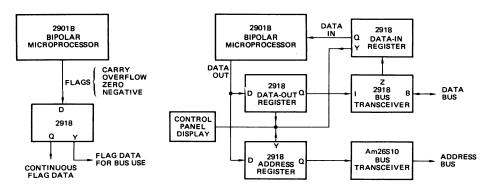

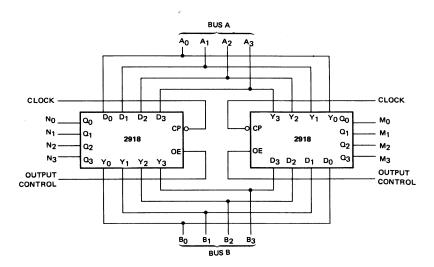

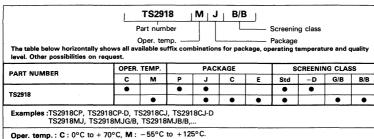

| ●TS2918 4-bit register                            | 163  |

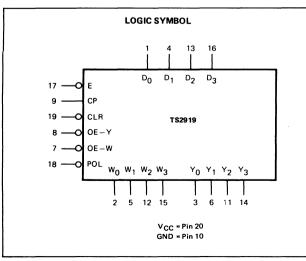

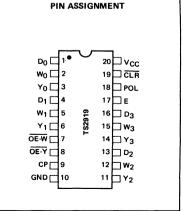

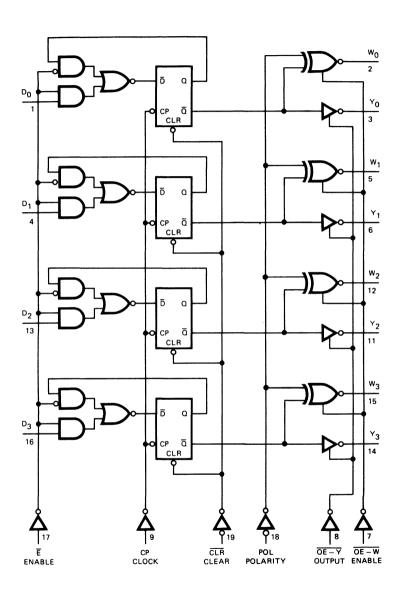

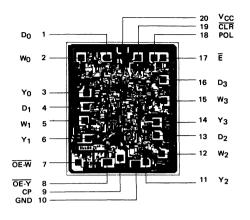

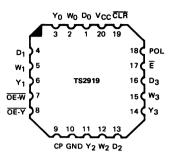

| ●TS2919 4-bit register                            | 171  |

| CHAPTER 3 - SEMI-CUSTOM ICs                       | 179  |

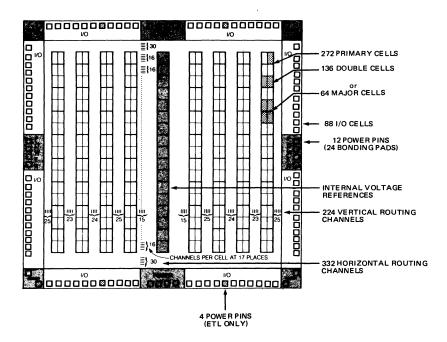

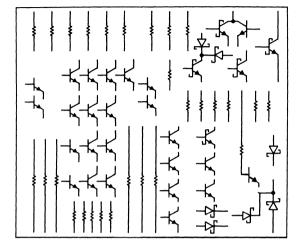

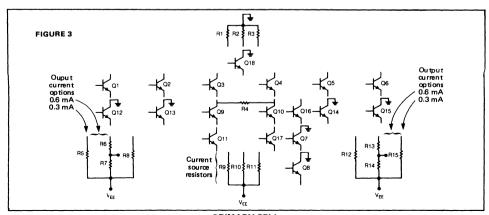

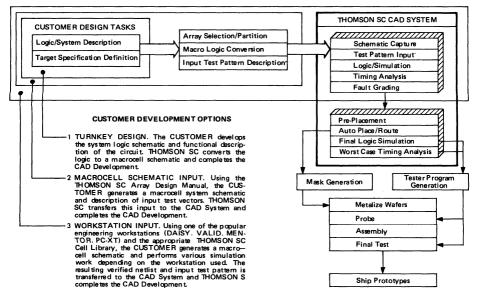

| TSC06/TSC12/TSC17 Bipolar macro arrays            | 181  |

| CHAPTER 4 - MILITARY AND HI-REL ICs               | 189  |

| CHAPTER 5 - QUALITY INFORMATION                   | 201  |

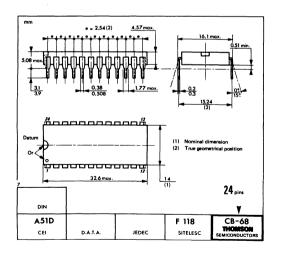

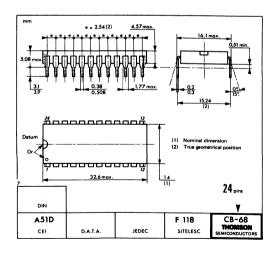

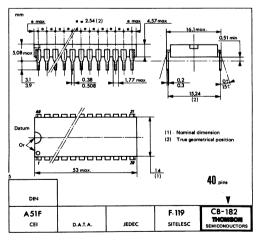

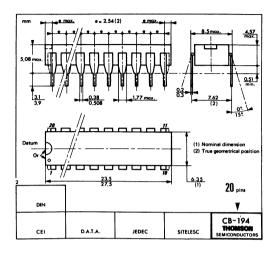

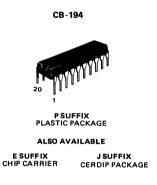

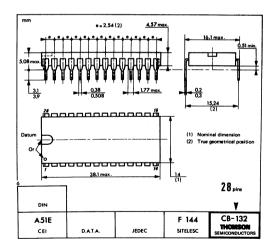

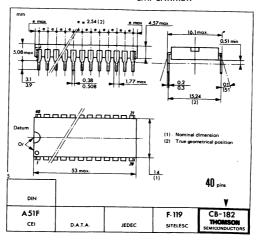

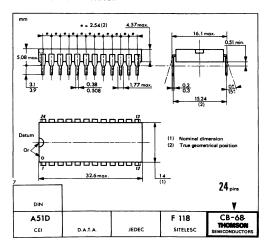

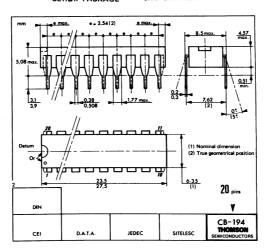

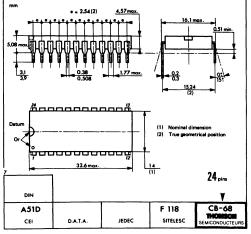

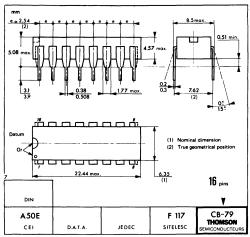

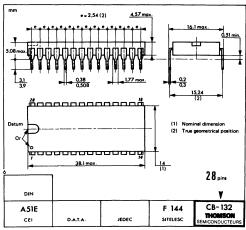

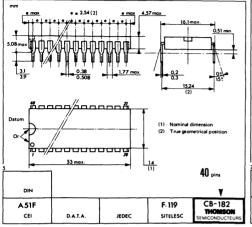

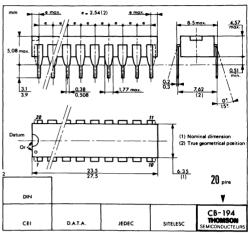

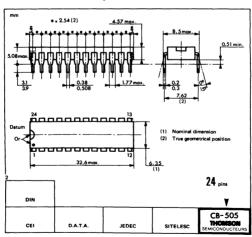

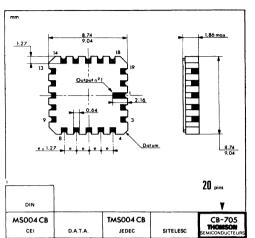

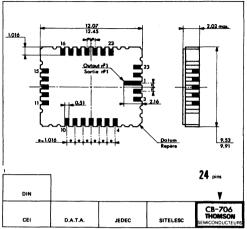

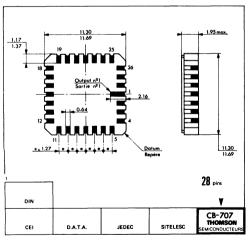

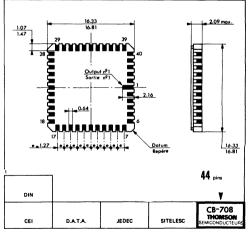

| CHAPTER 6 - PACKAGE DIMENSIONS                    | 217  |

| CHAPTER 7 - ORDERING INFORMATION                  | 221  |

<sup>•</sup> Hi-Rel versions available - See chapter 4

**Bipolar memories**

### **BIPOLAR MEMORY CROSS REFERENCE**

| PROM<br>Kbytes | AMD     | FAIRCHILD | FUJITSU | HARRIS | ммі     | NS     | SIGNETICS | TEXAS  | THOMSON<br>SC |

|----------------|---------|-----------|---------|--------|---------|--------|-----------|--------|---------------|

|                | 27S181  | 93Z451    | 7132    | 7681   | 6381    |        | 82S181A   | _      | TS71181A      |

| 8 K            | 27S181A | -         | _       | _      |         | _      | 82S181B   | _      | TS71181B      |

| 0 1            | _       | -         | -       | -      | -       | -      | -         | -      | TS71181C      |

|                | 27S281A | _         | -       | _      |         | _      | -         |        | TS71281C      |

|                | _       | -         | _       | _      | -       | _      | 82S191    | _      | TS71191       |

|                | 27S191  | 93Z511    | 7138    | 76161  |         | 87S191 | 82S191A   | 28S166 | TS71191A      |

| 16 K           | _       | -         | -       | -      | -       | -      | _         | -      | TS71191B      |

|                | 27S191A | -         | -       | _      | 631681  | _      | -         | -      | TS71191C      |

|                | 27S291A | _         | -       |        |         | -      | _         | _      | TS71291C      |

| 32 K           | _       | _         | 7142    | 76321  | 63S3281 | _      | 825321    | _      | TS71321C      |

| 64 K           | 27S49   | -         | 7143    | 76641  | _       | _      | _         | _      | TS71641       |

# THOMSON SEMICONDUCTEURS

TS71180 TS71181 TS71280 TS71281

#### PRODUCT PREVIEW

#### **8 K FAST PROMs**

The TS71180, 71181, 71280, 71281 are programmable read-only memories (PROM) organized in 1024 words by 8-bit configuration and are field programmable. They are shipped in an unprogrammed form and have "O" in all locations.

These PROM's are available with open collector (TS71180/71280) or three state outputs (TS71181/71281).

Fast access times :

Address access time: 25 ns max (TS71180C-71181C-71280C-71281C) 35 ns max (TS71180B-71181B-71280B-71281B)

45 ns max (TS71180A-71181A-71280A-71281A)

- Low voltage programming

- Highly reliable fuses Ti/W for ultra-fast programming

- Low power Schottky technology (oxide isolation process)

- TTL compatible

- Industry standard pin configuration.

#### **APPLICATIONS**

- Microprogramming

- Hardwired algorithms

- Random logic

- Code conversion

- Sequential controllers

**8 K FAST PROMs**

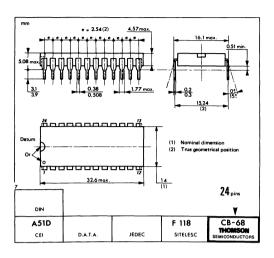

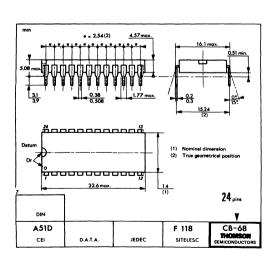

CASES CB-68 TS71180 TS71181 P SUFFIX LASTIC PACKAGE ALSO AVAILABLE **J SUFFIX** CSUFFIX CERDIP PACKAGE CERAMIC PACKAGE CB-505 TS71280 TS71281 **PSUFFIX** PLASTIC PACKAGE ALSO AVAILABLE

JSUFFIX

CERDIP PACKAGE

#### PIN ASSIGNMENT 24 7 VCC A7 🛮 1 23 A8 А5 Пз 22 T A9 21 CE1 A4 🗆 4 20 | CE2 АЗ ∏5 A2 | 6 19 CE3 A1 [7 18 CE4 A0 ∐8 17 08 01 🛮 9 16 7 07 02 110 15 7 06 03 🛮 11 14 7 05 GND 12 13 7 04 VCC : Power supply voltage (DC + 5 V) O1 to O8 : Outputs.

C SUFFIX

CERAMIC PACKAGE

#### THOMSON SEMICONDUCTEURS

Sales headquarters 45, av. de l'Europe - 78140 VELIZY - FRANCE Tel. : (1) 39.46.97.19 / Telex : 204780 F

#### **MAXIMUM RATINGS**

| Rating                | Symbol           | C suffix    | M suffix    | Unit |

|-----------------------|------------------|-------------|-------------|------|

| Power supply          | v <sub>cc</sub>  | 5 ± 5 %     | 5 ± 10 %    | v    |

| Operating temperature | Toper            | - 0, + 70   | - 55, + 125 | °C   |

| Storage temperature   | T <sub>stg</sub> | - 65, + 150 | - 65, + 150 | °c   |

#### **ELECTRICAL CHARACTERISTICS**

T<sub>amb</sub> = 25°C (unless otherwise noted)

| Characteristic                                                                                                                                  |                 |      | C suffi | ×      | ı    | Unit |        |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---------|--------|------|------|--------|----|

|                                                                                                                                                 |                 | Min  | Тур     | Max    | Min  | Тур  | Max    |    |

| Maximum input current at V <sub>OL</sub> max (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> =0.45 V)                                    | HL              | -    | -       | - 0.25 | -    | -    | - 0.25 | mA |

| Maximum input current at V <sub>IH</sub> min (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 2.7)                                      | ΙΉ              | l -  | _       | 40     | _    | - T  | 40     | μА |

| Maximum input current (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 5.5 V)                                                           | ЧR              | -    | _       | 40     | _    | _    | 50     | μΑ |

| Low level input voltage                                                                                                                         | VIL             | -    | -       | 0.8    | -    | _    | 0.8    | ٧  |

| High level input voltage                                                                                                                        | VIH             | 2    | -       |        | 2    | -    | -      | ٧  |

| Short-circuit output current (VCC= VCC max, VO= 0) (Note 1)                                                                                     | Isc             | - 20 | -       | - 70   | - 15 | -    | - 85   | mA |

| Low level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, I <sub>OL</sub> = 16 mA, V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> ) | VOL             | -    | -       | 0.45   | _    | _    | 0.5    | ٧  |

| High level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, I <sub>OH</sub> = 2 mA, V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> ) | Voн             | 2.4  | -       | -      | 2.4  | -    | -      | V  |

| Power supply current (All inputs are grounded VCC = VCC max)                                                                                    | <sup>1</sup> cc | -    |         | 175    | -    | -    | 185    | mA |

| Clamping input voltage (V <sub>CC</sub> = V <sub>CC</sub> min, V <sub>I</sub> = -18 mA)                                                         | ٧ı              | -    | -       | - 1.2  | -    | -    | - 1.2  | ٧  |

| Output leakage current (VCC = VCC max, CE1 = 2.4 V, CE2 = CE3 = 0.4 V)                                                                          |                 |      |         |        |      |      |        |    |

| V <sub>O</sub> = 5.5 V 71180/71280                                                                                                              | IOFF            | -    | -       | + 40   | _    | -    | + 60   | μΑ |

| V <sub>O</sub> = 5.5 V 71181/71281                                                                                                              | lozн            | - 1  | -       | + 40   | -    | -    | + 60   | μΑ |

| V <sub>O</sub> = 0.5 V 71181/71281                                                                                                              | lozL            | -    | -       | - 40   | -    | -    | - 60   | μΑ |

| Input capacitance (V <sub>I</sub> = 2 V @ f= 1 MHz) (Note 2)                                                                                    |                 | -    | 5       | -      | _    | 5    | _      | pF |

| Output capacitance (V <sub>j</sub> = 2 V @ f= 1 MHz) (Note 2)                                                                                   | co              | -    | 8       | -      | _    | 8    | -      | pF |

Note 1 : Only one output should be shorted at a time, otherwise permanent damage to the device may result.

Note 2 : These parameters are not 100 % tested, but are periodically sampled.

#### SWITCHING CHARACTERISTICS (These times are measured from threshold to threshold)

| Characteristic                                                                                                             |        | C suffix |             |                |             | Unit        |                |    |

|----------------------------------------------------------------------------------------------------------------------------|--------|----------|-------------|----------------|-------------|-------------|----------------|----|

| Ollaracteristic                                                                                                            | Symbol | Min      | Тур         | Max            | Min         | Тур         | Max            | 0  |

| Address access time $(A0-A9) \rightarrow (O1O8)$                                                                           | tAA    |          |             |                |             |             |                | ns |

| TS71180A, TS71181A, TS71280A, TS71281A<br>TS71180B, TS71181B, TS71280B, TS71281B<br>TS71180C, TS71181C, TS71280C, TS71281C |        | -<br> -  | _<br>_<br>_ | 45<br>35<br>25 | -<br>-<br>- | _<br>_<br>_ | 70<br>50<br>30 |    |

| Chip enable access time $(\overline{CE1}, \overline{CE2}, CE3, CE4) \rightarrow (O1O8)$                                    | tCE    |          |             |                |             |             |                | ns |

| TS71180A, TS71181A, TS71280A, TS71281A<br>TS71180B, TS71181B, TS71280B, TS71281B<br>TS71180C, TS71181C, TS71280C, TS71281C |        | -        | =           | 30<br>25<br>20 | -<br>-<br>- | _<br>_<br>_ | 40<br>30<br>25 |    |

| Chip disable time $(\overline{CE1}, \overline{CE2}, CE3, CE4) \rightarrow (O1O8)$                                          | tCD    |          |             |                |             |             |                | nš |

| TS71180A, TS71181A, TS71280A, TS71281A<br>TS71180B, TS71181B, TS71280B, TS71281B<br>TS71180C, TS71181C, TS71280C, TS71281C |        |          | -<br>-<br>- | 30<br>25<br>20 | _           | _<br>_<br>_ | 40<br>30<br>25 |    |

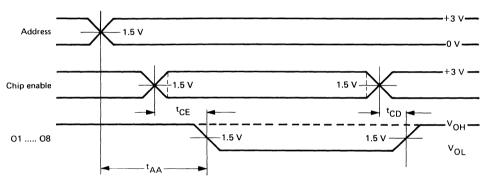

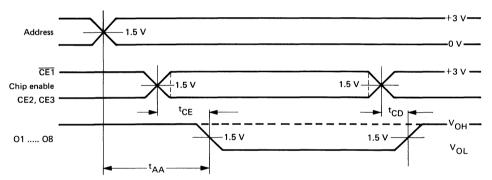

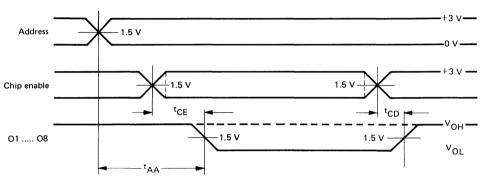

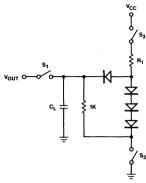

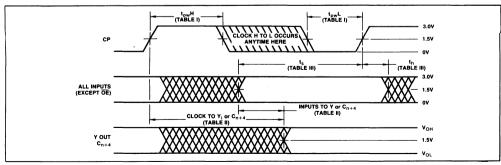

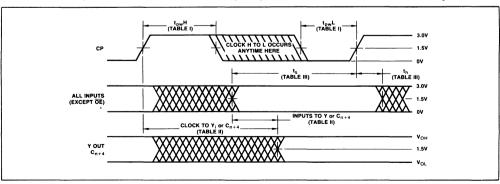

#### READING SEQUENCE

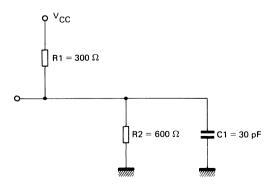

#### **DYNAMIC TEST**

#### PROGRAMMING CHARACTERISTICS

| Characteristic                                                     | Symbol          | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------|-----------------|------|-----|------|------|

| V <sub>CC</sub> programming pulse                                  | VCCP            | 12.5 | -   | 13   | V    |

| V <sub>CC</sub> during verify                                      | VCCL            | 4.5  | -   | -    | V    |

|                                                                    | Vccн            | -    | _   | 5.5  | V    |

| Programming supply current (V <sub>CCP</sub> = 12.75 $\pm$ 0.25 V) | ICCP            | -    | 420 | 550  | mA   |

| Input voltage                                                      | VIL             | 0    | -   | 0.5  | ٧    |

|                                                                    | VIН             | 2.4  | -   | 5.5  | V    |

| Output programming voltage                                         | v <sub>o</sub>  | 11.5 | 12  | 12.5 | V    |

| Output programming current (VO= 12 ± 0.5)                          | lo              | -    | 1.5 | -    | mA   |

| V <sub>CC</sub> pulse rise time                                    | <sup>t</sup> R1 | 5    | -   | 10   | μs   |

| Output pulse rise time                                             | <sup>t</sup> R2 | 10   | -   | 20   | μς   |

| CE1 programming pulse width                                        | tp              | 40   | 50  | 60   | μs   |

| Address set-up time / V <sub>CCP</sub>                             | <sup>t</sup> DA | 100  | -   | -    | ns   |

| Pulse sequence delay                                               | t <sub>D</sub>  | 10   | -   | -    | μς   |

| Delay time before verify                                           | tDV             | 3    | -   | -    | μs   |

| Programming time (V <sub>CC</sub> = V <sub>CCP</sub> )             | <sup>t</sup> PR | -    | -   | 10   | s    |

| Allowed fusing attempts                                            |                 | -    | · - | 1    |      |

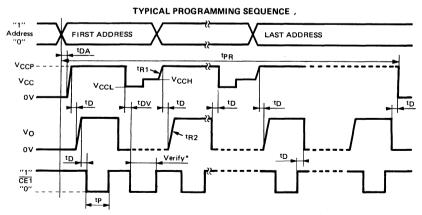

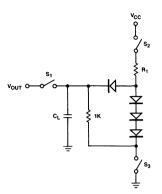

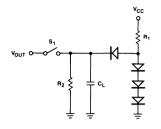

- 1. Select the address to be programmed. Apply  $\overline{CE1} = H$ ; CE2 = H; CE3 = H.

- 2. After a delay  $t_{DA} \geqslant$  100 ns, raise  $V_{CC}$  to  $V_{CCP} =$  12.75 V  $\pm$  0.25 V.

- 3. After a delay  $t_D \geqslant 10~\mu s$ , apply  $V_O = 12 \pm 0.5~V$  to the output to be programmed. Program one output at the time. Other outputs are open.

- 4. After a delay tp  $\geq$  10  $\mu$ s, apply a logic low level to the  $\overline{CE1}$  input. This level will be held during tp = 50  $\pm$  10  $\mu$ s.

- After a delay tp ≥ 10 µs, remove output voltage V<sub>O</sub> from the output to be programmed.

- 6. After a delay tp  $\geqslant$  10  $\mu\text{s}$ , lower the voltage VCCP to VCC = 5  $\pm$  0.5 V.

- 7. After a delay  $t_{DV} \ge 3 \mu_s$ , apply a logic low level to the  $\overline{\text{CE1}}$  input and verify that the programmed output remains in the high state for  $V_{CCH} = 5.5 \text{ V}$  and  $V_{CCL} = 4.5 \text{ V}$  (\*). Then, apply a logic high level to the  $\overline{\text{CE1}}$  chip select input.

- Repeat steps 1 through 7 to program other locations of the PROM.

\* Programming verification at both max and min VCC is optional (VCCH, VCCL).

#### CASES

CERAMIC PACKAGE

ALSO AVAILABLE

J SUFFIX

CERDIP PACKAGE

C SUFFIX

CB-505

TS71280

TS71281

C SUFFIX

CERAMIC PACKAGE

ALSO AVAILABLE

JSUFFIX

P SUFFIX

CERDIP PACKAGE

PLASTIC PACKAGE

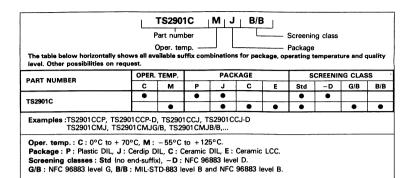

#### ORDERING INFORMATION

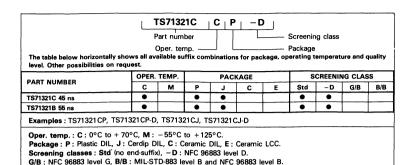

|                                                                                                                                                            | TS71181C    | C P O   |                                     |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-------------------------------------|--|--|--|--|--|--|--|--|

|                                                                                                                                                            | Part number |         | <ul> <li>Screening class</li> </ul> |  |  |  |  |  |  |  |  |

|                                                                                                                                                            | Oper. temp  | J L     | - Package                           |  |  |  |  |  |  |  |  |

| The table below horizontally shows all available suffix combinations for package, operating temperature and quality level. Other possibilities on request. |             |         |                                     |  |  |  |  |  |  |  |  |

| OPER                                                                                                                                                       | . TEMP.     | PACKAGE | SCREENING CLASS                     |  |  |  |  |  |  |  |  |

| PART NUMBER |                     | OPER. TEMP. |   |   | PACKAGE |   |   |     | SCREENING CLASS |     |     |  |

|-------------|---------------------|-------------|---|---|---------|---|---|-----|-----------------|-----|-----|--|

| 1           | PART NUMBER         | С           | М | Р | J       | С | E | Std | ~D              | G/B | B/B |  |

| 45 ns       | TS71180A, TS71181A  | •           |   | • | •       |   |   | •   | •               |     |     |  |

| 40 115      | TS71280A, TS71281A  | •           |   | • | •       |   |   | •   | •               |     |     |  |

| 35 ns       | TS71180B, TS71181B  | •           |   | • | •       |   |   | •   | •               |     |     |  |

| 35 HS       | TS71280B, TS71281B, | •           |   | • | •       |   |   | •   | •               |     |     |  |

| 25 ns       | TS71180C, TS71181C  | •           |   | • | •       |   |   | •   | •               |     |     |  |

| 25 118      | TS71280C, TS71281C  | •           |   | • | •       |   |   | •   | •               |     |     |  |

Examples: TS71181CP, TS71181CP-D, TS71181CJ, TS71181CJ-D

Oper. temp.: C:0°C to +70°C, M: -55°C to +125°C.

Package: P: Plastic DIL, J: Cerdip DIL, C: Ceramic DIL, E: Ceramic LCC.

Screening classes: Std (no end-suffix), -D: NFC 96883 level D.

G/B: NFC 96883 level G, B/B: MIL-STD-883 level B and NFC 96883 level B.

This is advance information on a new product. Specifications and information herein are subject to change without notice.

Please inquire with our sales offices about the availability of the different packages.

# **THOMSON** SEMICONDUCTEURS

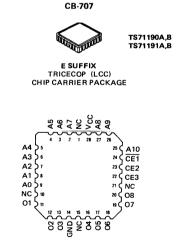

TS71190 TS71191 TS71290 TS71291

#### ADVANCE INFORMATION

#### 16 K FAST PROMs

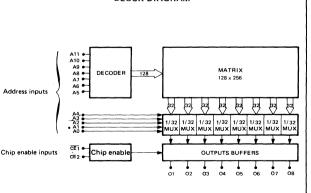

The TS71190, 71191, 71290, 71291 are programmable read-only memories (PROM) organized in a 2048 words by 8-bit configuration and are field programmable. They are shipped in an unprogrammed form and have "O" in all locations.

These PROM's are available with open collector (TS71190/71290) or three state outputs (TS71191/71291).

Fast access times :

Address access time: 80 ns max. (TS71190, TS71191)

60 ns max. (TS71190A, TS71191A) 45 ns max. (TS7190B, TS71191B)

35 ns max. (TS71190C, TS71191C)

(TS71290C, TS71291C)

- Temperature compensating circuits to achieve a wide range of operation Low voltage programming

- Highly reliable fuses Ti/W for ultra-fast programming

- Low power Schottky technology

- TTL compatible

- Industry standard pin configuration.

#### APPLICATIONS

- Microprogramming

- Hardwired algorithms Random logic

- Code conversion

Sequential controllers

16 K FAST **PROMs**

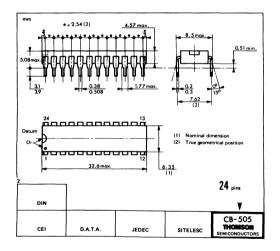

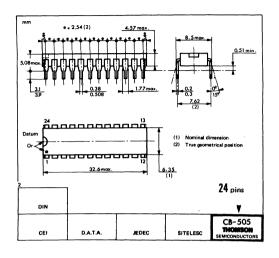

CASES **CB-68** CB 505 TS71290C

> P SUFFIX PLASTIC PACKAGE

ALSO AVAILABLE **J SUFFIX**

C SUFFIX CERAMIC PACKAGE CERDIP PACKAGE

TS71191A,B

TS71291C

E SUFFIX TRICECOP (LCC) CHIP CARRIER PACKAGE

Hi-Rel versions available - See chapter 4

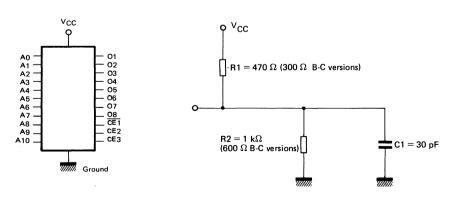

#### PIN ASSIGNMENT 24 | VCC A7 🗖 1 23 A A8 22 T A9 A5 ∐3 A4 🛮 4 21 T A10 20 T CE 1 АЗ ПБ A2 ∏6 19 CE2 A1 []7 18 CE3 17 08 A0 ∏8 01 🛮 9 16 7 07 02 110 15 7 06 14 05 03 🛮 11 GND 12 13 7 04 A0 to A10 : Address inputs CE1, CE2, CE3 : Chip enable inputs

Vcc : Power supply voltage (DC + 5 V) O1 to O8 : Outputs.

#### THOMSON SEMICONDUCTEURS

Sales headquarters 45, av. de l'Europe - 78140 VELIZY - FRANCE Tel. : (1) 39.46.97.19 / Telex : 204780F

#### MAXIMUM RATINGS

| Rating                | Symbol           | C suffix    | M suffix    | Unit |

|-----------------------|------------------|-------------|-------------|------|

| Power supply          | vcc              | 5 ± 5 %     | 5 ± 10 %    | v    |

| Operating temperature | Toper            | - 0, + 70   | - 55, + 125 | °C   |

| Storage temperature   | T <sub>stg</sub> | - 65, + 150 | - 65, + 150 | °c   |

#### **ELECTRICAL CHARACTERISTICS**

T<sub>amb</sub> = 25°C (unless otherwise noted)

| Characteristic                                                                                                                               |                                                                                                                     | Symbol                | ,            | C suffi | ×                    |      | M suffi | x                    | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|---------|----------------------|------|---------|----------------------|----------|

|                                                                                                                                              |                                                                                                                     |                       | Min          | Тур     | Max                  | Min  | Тур     | Max                  |          |

| Maximum input current at VOL max (VCC= V                                                                                                     | CC max, V <sub>I</sub> = 0.45 V)                                                                                    | IJL                   |              | _       | - 0.25               | _    | -       | - 0.25               | mA       |

| Maximum input current at VIH min (VCC= VC                                                                                                    | C max, V <sub>1</sub> = 2.7)                                                                                        | ΊΗ                    | -            | _       | 40                   | -    | -       | 40                   | μΑ       |

| Maximum input current (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> =                                                               | 5.5 V)                                                                                                              | l <sub>IR</sub>       | -            | -       | 40                   | _    | _       | 50                   | μΑ       |

| Low level input voltage                                                                                                                      |                                                                                                                     | VIL                   | _            | _       | 0.8                  | _    | _       | 0.8                  | ٧        |

| High level input voltage                                                                                                                     |                                                                                                                     | VIH                   | 2            | -       | _                    | 2    | -       | -                    | ٧        |

| Short-circuit output current (Note 1) VCC = VCC max, VO = 0                                                                                  | 71191,A,B,C<br>71291                                                                                                | Isc                   | - 20         | -       | - 70                 | - 15 | _       | - 85                 | mA       |

| Low level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> )<br>71190,A            |                                                                                                                     | VOL                   | _            | 0.35    | 0.45                 | -    | 0.35    | 0.5                  | v        |

| I <sub>OL</sub> = 16 mA                                                                                                                      | 71190B,C<br>71191B,C<br>71290C<br>71291C                                                                            |                       | _            | 0.35    | 0.45                 | -    | 0.35    | 0.5                  | V        |

| High level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, I <sub>OH</sub>                                                            | 4 = 2 mA, VI = VIH or VIL)                                                                                          | VOH                   | 2.4          | _       | -                    | 2.4  | -       | -                    | v        |

| Power supply current (All inputs are grounded                                                                                                | V <sub>CC</sub> = V <sub>CC</sub> max)                                                                              | <sup>1</sup> CC       | _            | 135     | 175                  | -    | 135     | 185                  | mA       |

| Clamping input voltage (V <sub>CC</sub> = V <sub>CC</sub> min, V <sub>I</sub> = -                                                            | -18 mA)                                                                                                             | ٧ı                    | -            | _       | - 1.2                |      | -       | - 1.2                | ٧        |

| Output leakage current ( $V_{CC} = V_{CC} \max \overline{CE1} = V_{O} = 5.5 \text{ V}$<br>$V_{O} = 5.5 \text{ V}$<br>$V_{O} = 0.5 \text{ V}$ | 2.4 V, CE <sub>2</sub> = CE <sub>3</sub> = 0.4 V)<br>71190,A,B,C/71290C<br>71191,A,B,C/71291C<br>71191,A,B,C/71291C | IOFF<br>IOZH          | -            | -       | + 40<br>+ 40<br>- 40 | -    |         | + 60<br>+ 60<br>- 60 | μΑ<br>μΑ |

|                                                                                                                                              | ote 2)                                                                                                              | OZL<br>C <sub>I</sub> | <del>-</del> | 5       | - 40                 | _    | 5       | - 60                 | μA<br>pF |

| Output capacitance (V <sub>I</sub> = 2 V @ f= 1 MHz) (No                                                                                     |                                                                                                                     | c <sub>O</sub>        |              | 8       | _                    | 1    | 8       | -                    | pF       |

Note 1: Only one output should be shorted at a time, otherwise permanent damage to the device may result.

Note 2: These parameters are not 100 % tested, but are periodically sampled.

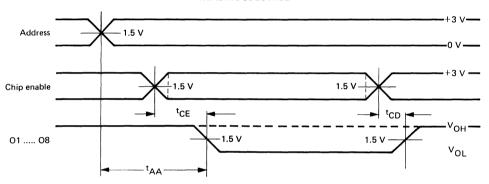

#### SWITCHING CHARACTERISTICS (These times are measured from threshold to threshold)

| Ch                      | aracteristic              | Symbol          |     | C suffix | (   | ı   | M suffi | ×   | Unit |

|-------------------------|---------------------------|-----------------|-----|----------|-----|-----|---------|-----|------|

|                         |                           |                 | Min | Тур      | Max | Min | Тур     | Max |      |

| Address access time     | (A0 - A10)(O1 O8)         | †AA             |     |          |     |     |         |     | ns   |

| TS71190 - TS71191       |                           |                 | -   | 40       | 80  | -   | 50      | 100 |      |

| TS71190A - TS71191A     |                           |                 | -   | 40       | 60  | Ì – | 50      | 80  |      |

| T\$71190B, T\$71191B    |                           |                 | -   | -        | 45  | -   |         | 65  |      |

| TS71190C, TS71191C )    |                           |                 | _   | _        | 35  | _   | l _     | 55  |      |

| TS71290C, TS71291C }    |                           |                 |     | }        |     |     |         |     |      |

| Chip enable access time | (CE1, CE2, CE3) → (O1 O8) | †CE             |     |          |     |     |         |     | ns   |

| TS71190,A/TS71191,A     |                           |                 | -   | 20       | 35  | -   | 20      | 45  |      |

| TS71190B, TS71191B      |                           |                 | -   | -        | 30  | -   |         | 35  |      |

| TS 71190C, TS 71191C    |                           |                 | l _ | _        | 25  | _   | _       | 30  |      |

| TS711290C, TS71291C     |                           |                 |     |          |     |     |         |     |      |

| Chip disable time       | (CE1, CE2, CE3)(O1 O8)    | t <sub>CD</sub> |     |          |     |     |         |     | ns   |

| TS71190,A/TS71191,A     |                           |                 | -   | 20       | 35  | -   | 20      | 45  |      |

| TS71190B, TS71191B      |                           |                 | -   | -        | 30  | -   | -       | 35  |      |

| TS71190C, TS71191C )    |                           |                 | _   | _        | 25  | _   | _       | 30  |      |

| TS71290C, TS71291C ∫    |                           |                 |     |          | -   |     | ĺ       |     |      |

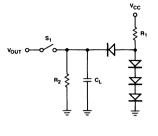

#### **READING SEQUENCE**

#### **DYNAMIC TEST**

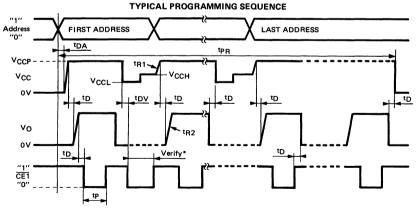

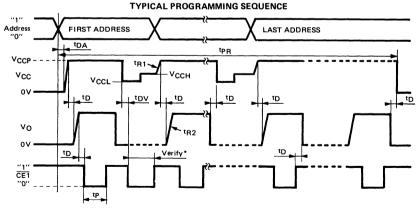

#### PROGRAMMING CHARACTERISTICS

| Characteristic                                                     | Symbol         | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------|----------------|------|-----|------|------|

| V <sub>CC</sub> programming pulse                                  | VCCP           | 12.5 | -   | 13   | V    |

| V <sub>CC</sub> during verify                                      | VCCL           | 4.5  | -   | -    | V    |

|                                                                    | Vccн           |      | _   | 5.5  | V    |

| Programming supply current (V <sub>CCP</sub> = 12.75 $\pm$ 0.25 V) | ICCP           | -    | 420 | 550  | mA   |

| Input voltage                                                      | VIL            | 0    | -   | 0.5  | V    |

|                                                                    | VIH            | 2.4  | -   | 5.5  | V    |

| Output programming voltage                                         | v <sub>o</sub> | 11.5 | 12  | 12.5 | V    |

| Output programming current (V <sub>O</sub> = 12 ± 0.5)             | lo             | -    | 1.5 | -    | mA   |

| V <sub>CC</sub> pulse rise time                                    | tR1            | 5    | -   | 10   | μs   |

| Output pulse rise time                                             | tR2            | 10   | -   | 20   | μs   |

| CE <sub>1</sub> programming pulse width                            | tp             | 40   | 50  | 60   | μs   |

| Address set-up time / V <sub>CCP</sub>                             | tDA            | 100  | -   | -    | ns   |

| Pulse sequence delay                                               | t <sub>D</sub> | 10   | -   | -    | μs   |

| Delay time before verify                                           | tDV            | 3    | -   | -    | μs   |

| Programming time (V <sub>CC</sub> = V <sub>CCP</sub> )             | ŧРR            | -    | -   | 10   | s    |

| Allowed fusing attempts                                            |                | -    | -   | 1    |      |

- Select the address to be programmed.

Apply CE1 = H; CE2 = H; CE3 = H.

- 2. After a delay  $t_{DA} \ge 100$  ns, raise V<sub>CC</sub> to V<sub>CCP</sub> = 12.75 V  $\pm$  0.25 V.

- 3. After a delay  $t_D \geqslant 10~\mu s$ , apply  $V_O = 12 \pm 0.5~V$  to the output to be programmed. Program one output at the time. Other outputs are open.

- After a delay t<sub>D</sub> ≥ 10 μs, apply a logic low level to the CE1 input. This level will be held during tp = 50 ± 10 μs.

- 5. After a delay tp  $\geq$  10  $\mu$ s, remove output voltage VO from the output to be programmed.

- 6. After a delay tp  $\geqslant$  10  $\mu s$ , lower the voltage VCCP to VCC = 5  $\pm$  0.5 V.

- 7. After a delay  $t_{DV} \ge 3~\mu s$ , apply a logic low level to the  $\overline{\text{CE1}}$  input and verify that the programmed output remains in the high state for  $V_{CCH} = 5.5~V$  and  $V_{CCL} = 4.5~V$  (\*). Then, apply a logic high level to the  $\overline{\text{CE1}}$  chip select input.

- Repeat steps 1 through 7 to program other locations of the PROM.

\* Programming verification at both max and min VCC is optional (VCCH, VCCL).

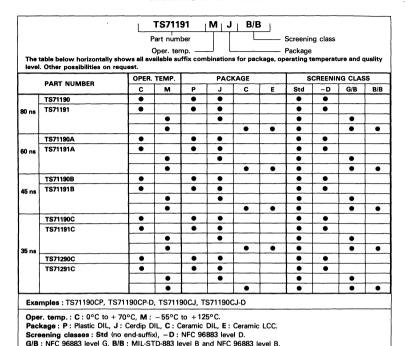

#### ORDERING INFORMATION

P SUFFIX

PLASTIC PACKAGE

ALSO AVAILABLE

C SUFFIX

J SUFFIX

CERAMIC PACKAGE

CERDIP PACKAGE

#### CASES

PLASTIC PACKAGE

ALSO AVAILABLE

C SUFFIX

CERAMIC PACKAGE

CEROIP PACKAGE

This is advance information and specifications are subject to change without notice. Please inquire with our sales offices about the availability of the different packages.

Printed in France

#### PRODUCT PREVIEW

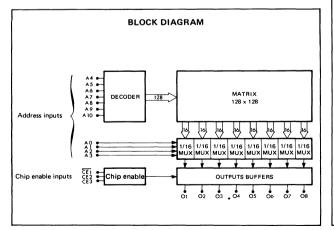

#### 32 K FAST PROMs

The TS71321 is programmable read-only memory (PROM) organized in a 4096 words by 8-bit configuration and is field programmable. It is shipped in an unprogrammed form and has "0" in all allocations. This PROM's is available with three state outputs (TS71321).

Fast access times :

Address access time: 45 ns max TS71321C

55 ns max TS71321B

- Low voltage programming

- Highly reliable fuses Ti/W for ultra-fast programming

- Low power Schottky technology (oxide isolation process)

- TTL compatible

- Industry standard pin configuration.

#### **APPLICATIONS**

- Microprogramming

- Hardwired algorithms

- Random logic

- Code conversion

- Sequential controllers

#### 32 K FAST **PROMs**

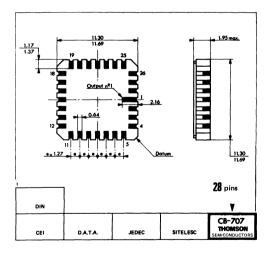

CASE CB-68

P SUFFIX PLASTIC PACKAGE

ALSO AVAILABLE JSUFFIX **C SUFFIX** CERDIP PACKAGE CERAMIC PACKAGE

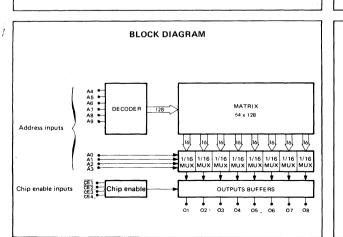

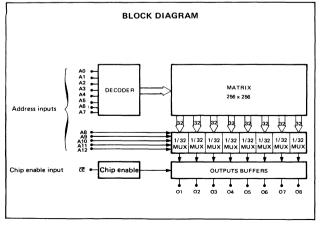

### **BLOCK DIAGRAM**

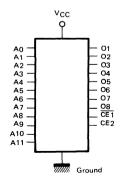

#### PIN ASSIGNMENT

| A7 [  | 1 0 | 24 🗍 VCC |

|-------|-----|----------|

| A6 [  | 2   | 23 A8    |

| A5 [  | 3   | 22 🗍 A9  |

| A4 [  | 4   | 21 A10   |

| A3 [  | 5   | 20 CE1   |

| A2 [  | 6   | 19 A 1 1 |

| A1 [  | 7   | 18 CE2   |

| A0 [  | 8   | 17 08    |

| 01 [  | 9   | 16 07    |

| 02    | 10  | 15 06    |

| О3 [  | 11  | 14 🗍 05  |

| GND [ | 12  | 13 04    |

|       | L   |          |

Vcc : Power supply voltage (DC + 5 V) O1 to O8 : Outputs.

#### THOMSON SEMICONDUCTEURS

Sales headquarters 45, av. de l'Europe - 78140 VELIZY - FRANCE Tei. : (1) 39.46.97.19 / Telex : 204780F

#### **MAXIMUM RATINGS**

| Rating                | Symbol           | C suffix    | M suffix    | Unit |

|-----------------------|------------------|-------------|-------------|------|

| Power supply          | vcc              | 5 ± 5 %     | 5 ± 10 %    | V    |

| Operating temperature | Toper            | - 0, + 70   | - 55, + 125 | °C   |

| Storage temperature   | T <sub>stg</sub> | - 65, + 150 | - 65, + 150 | °c   |

#### **ELECTRICAL CHARACTERISTICS**

Tamb = 25°C (unless otherwise noted)

| Characteristic                                                                                                                                  | Symbol           | ,    | C suffi: | ×      | -    | VI suffi | ×      | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|----------|--------|------|----------|--------|----------|

| ,                                                                                                                                               |                  | Min  | Тур      | Max    | Min  | Тур      | Max    |          |

| Maximum input current at V <sub>OL</sub> max (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> =0.45 V)                                    | l <sub>I</sub> L | _    | -        | - 0.25 | 1    | -        | - 0.25 | mA       |

| Maximum input current at V <sub>IH</sub> min (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 2.7)                                      | ΊΗ               | _    | _        | 40     | -    | _        | 40     | μΑ       |

| Maximum input current (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 5.5 V)                                                           | <sup>I</sup> IR  | -    | _        | 40     | -    | _        | 50     | μΑ       |

| Low level input voltage                                                                                                                         | VIL              | -    | -        | 0.8    | _    | -        | 0.8    | ٧        |

| High level input voltage                                                                                                                        | VIH              | 2    | -        | _      | 2    | _        | _      | ٧        |

| Short-circuit output current (VCC= VCC max, VO= 0) (Note 1)                                                                                     | Isc              | - 20 | -        | - 70   | - 15 | -        | - 85   | mA       |

| Low level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, I <sub>OL</sub> = 16 mA, V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> ) | VOL              | -    | -        | 0.45   | -    | -        | 0.5    | ٧        |

| High level output voltage (VCC = VCC min, IOH = 2 mA, VI = VIH or VIL)                                                                          | Voн              | 2.4  | _        | -      | 2.4  | _        | -      | <b>v</b> |

| Power supply current (All inputs are grounded VCC = VCC max)                                                                                    | Icc              | -    | _        | 175    | _    | -        | 185    | mA       |

| Clamping input voltage (V <sub>CC</sub> = V <sub>CC</sub> min, V <sub>I</sub> = -18 mA)                                                         | VI               | _    | -        | - 1.2  | -    | _        | - 1.2  | ٧        |

| Output leakage current (V <sub>CC</sub> = V <sub>CC</sub> max, CE1 = 2.4 V, CE2 = CE3 = 0.4 V)                                                  |                  |      |          |        |      |          |        |          |

| V <sub>O</sub> = 5.5 V                                                                                                                          | <sup>I</sup> OZH | -    | -        | + 40   | -    | _        | + 60   | μΑ       |

| $V_0 = 0.5 V$                                                                                                                                   | lozL             | -    | -        | - 40   | -    | _        | - 60   | μА       |

| Input capacitance (V <sub>I</sub> = 2 V @ f = 1 MHz) (Note 2)                                                                                   | CI               | _    | 5        | _      | -    | 5        | -      | pF       |

| Output capacitance (V <sub>I</sub> = 2 V @ f= 1 MHz) (Note 2)                                                                                   | co               |      | 8        | _      | _    | 8        | -      | p?       |

Note 1 : Only one output should be shorted at a time, otherwise permanent damage to the device may result.

Note 2: These parameters are not 100 % tested, but are periodically sampled.

#### PROGRAMMING CHARACTERISTICS

| Characteristic                                                     | Symbol          | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------|-----------------|------|-----|------|------|

| V <sub>CC</sub> programming pulse                                  | VCCP            | 12.5 | -   | 13   | V    |

| V <sub>CC</sub> during verify                                      | VCCL            | 4.5  | -   | -    | V    |

|                                                                    | Vccн            |      |     | 5.5  | V    |

| Programming supply current (V <sub>CCP</sub> = 12.75 $\pm$ 0.25 V) | ICCP            | -    | 420 | 550  | mA   |

| Input voltage                                                      | VIL             | 0    | -   | 0.5  | V    |

|                                                                    | ViH             | 2.4  |     | 5.5  | V    |

| Output programming voltage                                         | v <sub>o</sub>  | 11.5 | 12  | 12.5 | V    |

| Output programming current ( $V_0$ = 12 ± 0.5)                     | 10              | -    | 1.5 | -    | mA   |

| V <sub>CC</sub> pulse rise time                                    | tR1             | 5    | -   | 10   | μς   |

| Output pulse rise time                                             | tR2             | 10   | _   | 20   | μς   |

| CE <sub>1</sub> programming pulse width                            | tp              | 40   | 50  | 60   | μs   |

| Address set-up time / V <sub>CCP</sub>                             | <sup>t</sup> DA | 100  | -   | -    | ns   |

| Pulse sequence delay                                               | t <sub>D</sub>  | 10   | -   | -    | μς   |

| Delay time before verify                                           | <sup>t</sup> DV | 3    | -   | -    | μs   |

| Programming time (V <sub>CC</sub> = V <sub>CCP</sub> )             | tPR             | -    | -   | 10   | s    |

| Allowed fusing attempts                                            |                 | -    | -   | 1    |      |

- Select the address to be programmed.

Apply CE1 = H; CE2 = H; CE3 = H.

- 2. After a delay  $t_{DA} \ge 100$  ns, raise  $V_{CC}$  to  $V_{CCP} = 12.75 \text{ V} \pm 0.25 \text{ V}$ .

- 3. After a delay tp  $\geqslant$  10  $\mu$ s, apply V<sub>O</sub> = 12  $\pm$  0.5 V to the output to be programmed. Program one output at the time. Other outputs are open.

- 4. After a delay tp  $\geqslant$  10  $\mu$ s, apply a logic low level to the  $\overline{CE1}$  input. This level will be held during tp = 50  $\pm$  10  $\mu$ s.

- 5. After a delay tp  $\geqslant$  10  $\mu$ s, remove output voltage  $V_O$  from the output to be programmed.

- 6. After a delay tp  $\geqslant$  10  $\mu s$ , lower the voltage VCCP to VCC = 5  $\pm$  0.5 V.

- 7. After a delay tDV  $\geqslant$  3  $\mu$ s, apply a logic low level to the  $\overline{\text{CE1}}$  input and verify that the programmed output remains in the high state for V<sub>CCH</sub> = 5.5 V and V<sub>CCL</sub> = 4.5 V (\*). Then, apply a logic high level to the  $\overline{\text{CE1}}$  chip select input.

- 8. Repeat steps 1 through 7 to program other locations of the PROM.

<sup>\*</sup> Programming verification at both max and min  $V_{CC}$  is optional ( $V_{CCH}$ ,  $V_{CCL}$ ).

### SWITCHING CHARACTERISTICS (These times are measured from threshold to threshold)

| Charac                  | Characteristic      |                 | C suffix |     |          | M suffix |     |          | Unit |

|-------------------------|---------------------|-----------------|----------|-----|----------|----------|-----|----------|------|

|                         |                     | Symbol          | Min      | Тур | Max      | Min      | Тур | Max      | ""   |

| Address access time     | (A0-A11) → (O1O8)   | tAA             |          |     |          |          |     |          | ns   |

| TS71321B<br>TS71321C    |                     |                 | =        | _   | 55<br>45 | _        | _   | 65<br>60 |      |

| Chip enable access time | (CE1, CE2) → (O1O8) | <sup>†</sup> CE |          |     |          |          |     |          | ns   |

| TS71321B<br>TS71321C    |                     |                 | =        | =   | 35<br>20 | _        | _   | 40<br>30 |      |

| Chip disable time       | (CE1, CE2) → (O1O8) | tCD             |          |     |          |          |     |          | ns   |

| TS71321B<br>TS71321C    |                     |                 | =        | _   | 35<br>20 | _        | -   | 40<br>30 |      |

#### **READING SEQUENCE**

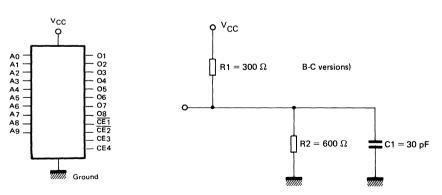

#### DYNAMIC TEST

4/5

#### ORDERING INFORMATION

P SUFFIX PLASTIC PACKAGE

ALSO AVAILABLE

J SUFFIX C SUFFIX

CERDIP PACKAGE CERAMIC PACKAGE

This is advance information and specifications are subject to change without notice. Please inquire with our sales offices about the availability of the different packages.

**NOTES**

# **THOMSON SEMICONDUCTEURS**

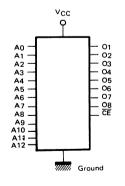

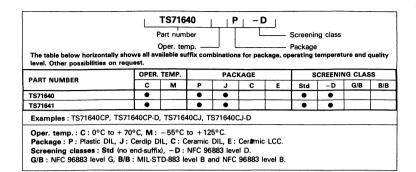

TS71640 TS71641

#### PRODUCT PREVIEW

#### 64 K FAST PROMs

The TS71640, 71641 are programmable read-only memories (PROM) organized in a 8192 words by 8-bit configuration and are field programmable. They are shipped in an unprogrammed form and have "0" in all allocations. These PROM's are available with open collector (TS71640) or three state outputs (TS71641).

Fast access times :

Address access time: 55 ns max. Enable access time: 30 ns max.

- Highly reliable shorting junction concept

- Low power Schottky technology (oxide isolation process)

- TTL compatible

- Industry standard pin configuration.

#### APPLICATIONS

- Microprogramming

- Hardwired algorithms

- Random logic

- Code conversion

- Sequential controllers

64 K FAST **PROMs**

CASE CB-68

C SUFFIX CERAMIC PACKAGE

#### PIN ASSIGNMENT A7 ∏1 23 A8 А6 Г A5 ∐3 22 A9 A4 🗆 4 21 A10 A3 ∏5 20 T CE A2 ☐6 19 A11 A1 [7 18 A12 Ао ∏в 17 7 08 01 🛮 9 16 7 07 02 110 15 7 06 оз П 11 14 7 05 GND 12 13 04 VCC : Power supply voltage (DC + 5 V) O1 to O8 : Outputs.

#### THOMSON SEMICONDUCTEURS

Sales headquarters 45, av. de l'Europe - 78140 VELIZY - FRANCE Tel. : (1) 39.46.97.19 / Telex : 204780F

#### MAXIMUM RATINGS

| Rating                | Symbol           | C suffix    | M suffix    | Unit |

|-----------------------|------------------|-------------|-------------|------|

| Power supply          | Vcc              | 5 ± 5 %     | 5 ± 10 %    | V    |

| Operating temperature | Toper            | - 0, + 70   | - 55, + 125 | °c   |

| Storage temperature   | T <sub>stg</sub> | - 65, + 150 | - 65, + 150 | °c   |

#### **ELECTRICAL CHARACTERISTICS**

Tamb = 25°C (unless otherwise noted)

| Characteristic                                                                                                                                  | Symbol           |      | C suffi | x      |      | VI suffi | ×      | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|---------|--------|------|----------|--------|------|

|                                                                                                                                                 |                  | Min  | Тур     | Max    | Min  | Тур      | Max    |      |

| Maximum input current at V <sub>OL</sub> max (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 0.45 V)                                   | HL               | -    | -       | - 0.25 | -    | _        | - 0.25 | . mA |

| Maximum input current at V <sub>IH</sub> min (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 2.7)                                      | ΉΗ               | -    | -       | 40     | _    | _        | 40     | μΑ   |

| Maximum input current (V <sub>CC</sub> = V <sub>CC</sub> max, V <sub>I</sub> = 5.5 V)                                                           | l <sub>IR</sub>  | _    | -       | 40     | _    | _        | 50     | μΑ   |

| Low level input voltage                                                                                                                         | VIL              | _    | _       | 0.8    | _    | -        | 0.8    | ٧    |

| High level input voltage                                                                                                                        | ViH              | 2    | _       | _      | 2    | -        | -      | V    |

| Short-circuit output current (VCC = VCC max, VO = 0) (Note 1)                                                                                   | <sup>I</sup> sc  | - 20 | -       | - 70   | - 15 | -        | - 85   | mA   |

| Low level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, I <sub>OL</sub> = 16 mA, V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> ) | VOL              | -    | -       | 0.45   | -    | -        | 0.5    | V    |

| High level output voltage (V <sub>CC</sub> = V <sub>CC</sub> min, I <sub>OH</sub> = 2 mA, V <sub>I</sub> = V <sub>IH</sub> or V <sub>IL</sub> ) | Voн              | 2.4  | -       | _      | 2.4  | _        | -      | ٧    |

| Power supply current (All inputs are grounded V <sub>CC</sub> = V <sub>CC</sub> max)                                                            | <sup>1</sup> CC  | _    | -       | 175    | -    | -        | 185    | mA   |

| Clamping input voltage (V <sub>CC</sub> = V <sub>CC</sub> min, V <sub>I</sub> = -18 mA)                                                         | V <sub>I</sub>   | -    | _       | - 1.2  | 1    | -        | - 1.2  | V    |

| Output leakage current (V <sub>CC</sub> = V <sub>CC</sub> max, CE1 = 2.4 V, CE2 = CE3 = 0.4 V)                                                  |                  |      |         |        |      |          |        |      |

| V <sub>O</sub> = 5.5 V 71640                                                                                                                    | IOFF             | -    | -       | + 40   | -    | _        | + 60   | μΑ   |

| V <sub>O</sub> = 5.5 V 71641                                                                                                                    | <sup>‡</sup> OZH | -    | -       | + 40   | -    | -        | + 60   | μΑ   |

| V <sub>O</sub> = 0.5 V 71641                                                                                                                    | IOZL             | -    | -       | - 40   | -    | -        | - 60   | μΑ   |

| Input capacitance (V <sub>j</sub> = 2 V @ f = 1 MHz) (Note 2)                                                                                   | Cl               | _    | 5       | _      | _    | 5        | _      | ρF   |

| Output capacitance (V <sub>I</sub> = 2 V @ f= 1 MHz) (Note 2)                                                                                   | СО               | -    | 8       | -      | -    | 8        | -      | pF   |

Note 1: Only one output should be shorted at a time, otherwise permanent damage to the device may result.

Note 2: These parameters are not 100 % tested, but are periodically sampled.

### SWITCHING CHARACTERISTICS (These times are measured from threshold to threshold)

| Characteristic          |                      | Symbol | C suffix |     |     | M suffix |     |     | Unit |

|-------------------------|----------------------|--------|----------|-----|-----|----------|-----|-----|------|

|                         |                      |        | Min      | Тур | Max | Min      | Тур | Max |      |

| Address access time     | (A0 - A12) → (O1 O8) | tAA    | _        | -   | 55  | -        | -   | 65  | ns   |

| Chip enable access time | ( CE ) → (O1 O8)     | tCE    | -        | -   | 30  | -        | -   | 35  | ns   |

| Chip disable time       | ( CE ) → (O1 O8)     | tCD    | -        | -   | 30  | -        | -   | 35  | ņs   |

#### READING SEQUENCE

#### DYNAMIC TEST

#### ORDERING INFORMATION

This is advance information and specifications are subject to change without notice. Please inquire with our sales offices about the availability of the different packages.

Bipolar microprocessor series

# THOMSON SEMICONDUCTEURS

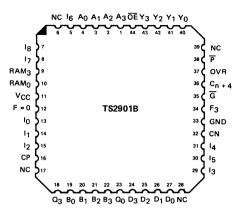

TS2901B

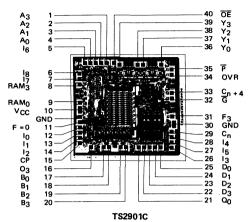

#### 4-BIT BIPOLAR MICROPROCESSOR SLICE

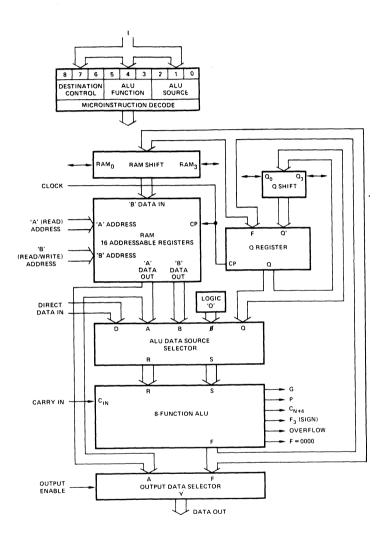

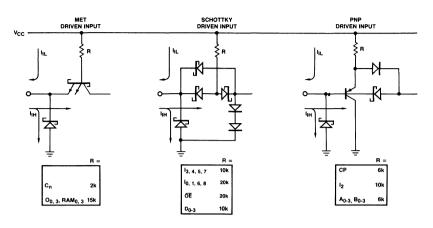

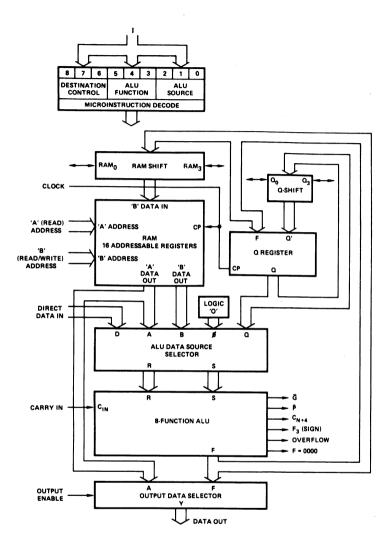

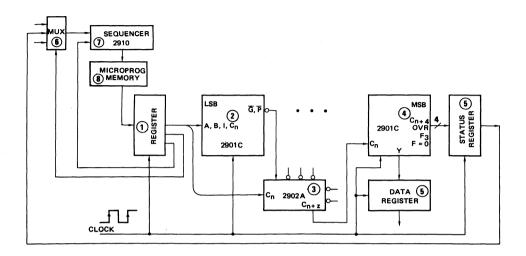

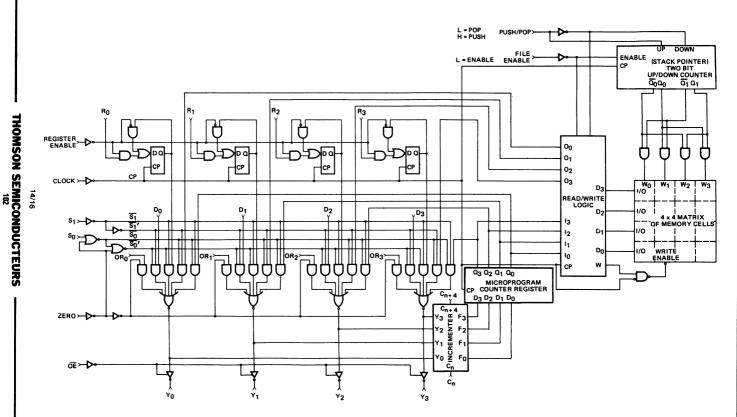

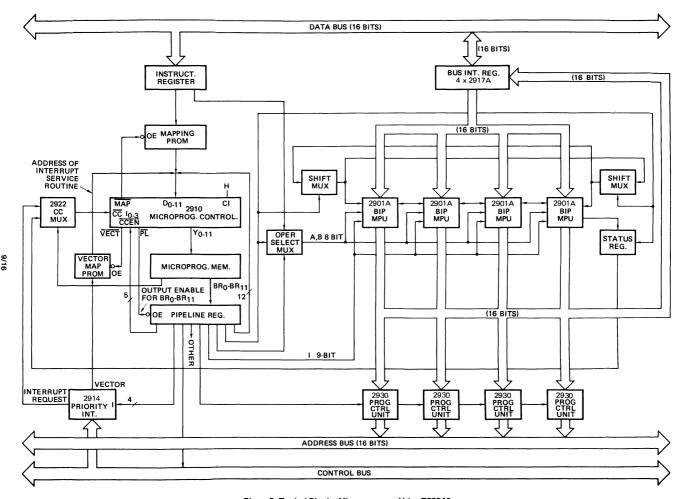

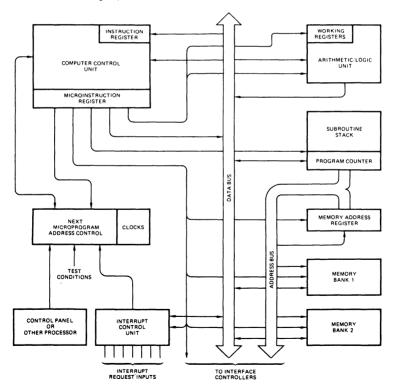

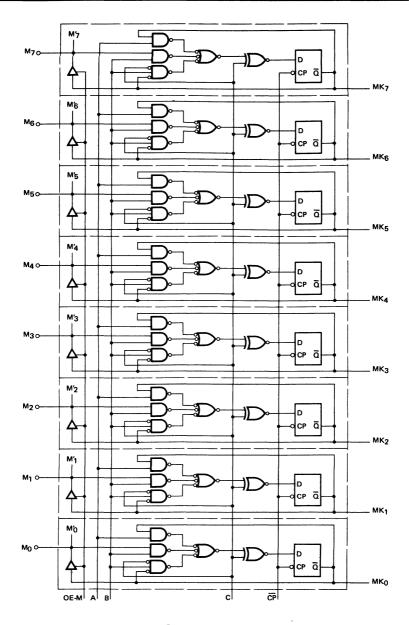

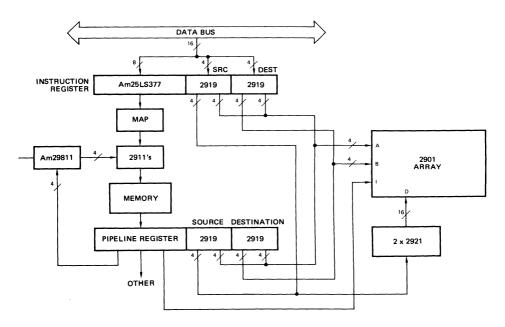

The four-bit bipolar microprocessor slice is designed as a high-speed cascadable element intended for use in CPU's, peripheral controllers, programmable microprocessors and numerous other applications. The microinstruction flexibility of the TS2901B will allow efficient emulation of almost any digital computing machine.

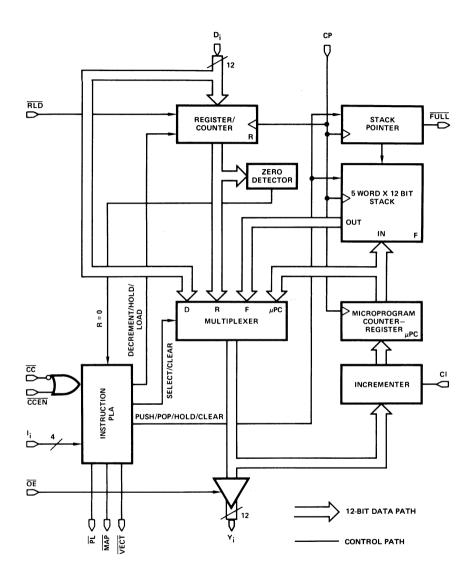

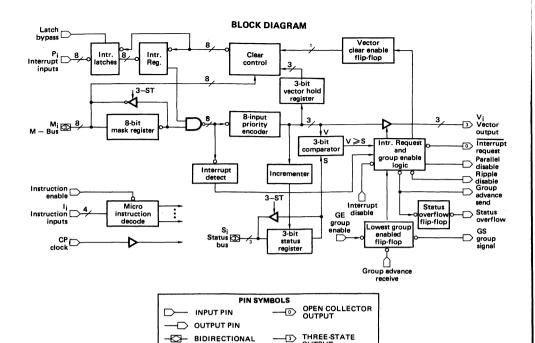

The device, as shown in the block diagram (next page), consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The nine-bit microinstruction word is organized into three groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The micro-processor is cascadable with full look-ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.

- Two-address architecture Independent simultaneous access to two working registers saves machine cycles.

- Eight-function ALU Performs addition, two subtraction operations, and five logic functions on two source operands.

- Flexible data source selection

ALU data is selected from five source parts for a total of 203 source

operand pairs for every ALU function.

- Left/right shift independent of ALU Add and shift operations take only one cycle.

- Four status flags

Carry, overflow, zero, and negative.

- Expandable.

- Connect any number of 2901's together for longer word lengths.

- Microprogrammable

- Three groups of three bits each for source operand, ALU function, and destination control.

For applications information see the last part of this data sheet and chap-

ters III and IV of Bit Slice Microprocessor Design, Mick & Brick.

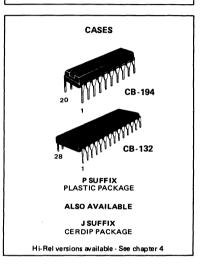

4-BIT BIPOLAR

MICROPROCESSOR SLICE

P SUFFIX

PLASTIC PACKAGE

ALSO AVAILABLE

1 J SUFFIX

CERDIP PACKAGE

Hi-Rel versions available - See chapter 4

f. 01210-R

#### THOMSON SEMICONDUCTEURS

#### **BLOCK DIAGRAM**

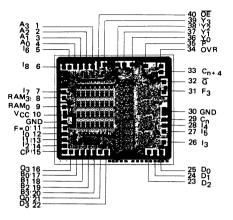

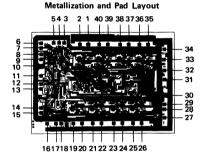

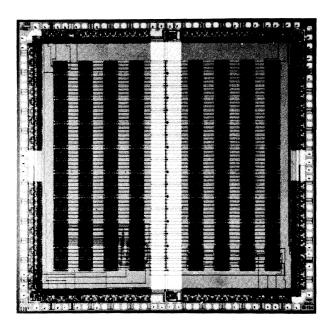

#### **METALLIZATION AND PAD LAYOUT**

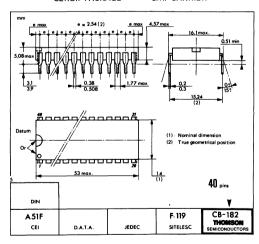

**TS2901B**Die size: 3.310 x 3.015 mm

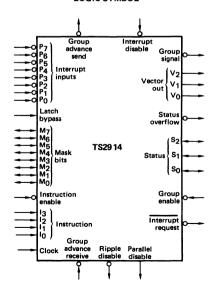

#### **CHIP CARRIER**

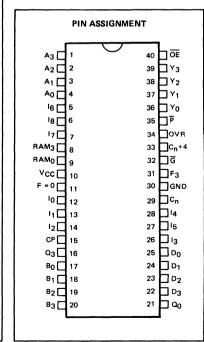

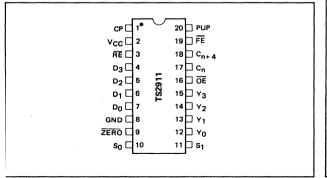

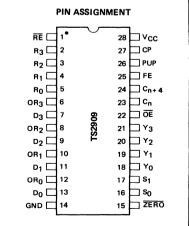

#### PIN DEFINITION

- ${\rm \textbf{A}}_{0\text{-}3}$  The four address inputs to the register stack used to select one register whose contents are displayed through the A-port.

- B<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the B-port and into which new data can be written when the clock goes LOW.

- $I_{0-8}$  The nine instruction control lines. Used to determine what data sources will be applied to the ALU ( $I_{012}$ ), what function the ALU will perform ( $I_{345}$ ), and what data is to be deposited in the Q-register or the register stack ( $I_{678}$ ).

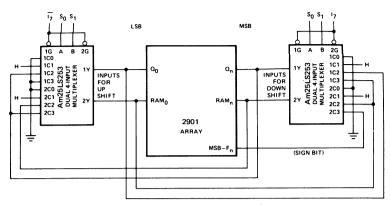

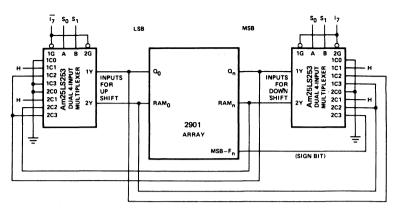

- Q<sub>3</sub> A shift line at the MSB of the Q register (Q<sub>3</sub>) and the RAM<sub>3</sub> register stack (RAM<sub>3</sub>). Electrically these lines are three-state outputs connected to TTL inputs internal to the device. When the destination code on I<sub>678</sub> indicates an up shift (octal 6 or 7) the three-state outputs are enabled and the MSB of the Q register is available on the Q<sub>3</sub> pin and the MSB of the ALU output is available on the RAM<sub>3</sub> pin. Otherwise, the three-state outputs are OFF (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5).

- Q<sub>0</sub> Shift lines like Q<sub>3</sub> and RAM<sub>3</sub>, but at the LSB of the RAM<sub>0</sub> Q-register and RAM. These pins are tied to the Q<sub>3</sub> and RAM<sub>3</sub> pins of the adjacent device to transfer data between devices for up and down shifts of the Q register and ALU data.

- $\begin{array}{c} \textbf{D}_{0\text{-}3} & \text{Direct data inputs. A four-bit data field which may be} \\ & \text{selected as one of the ALU data sources for entering data} \\ & \text{into the device. } \textbf{D}_0 \text{ is the LSB.} \end{array}$

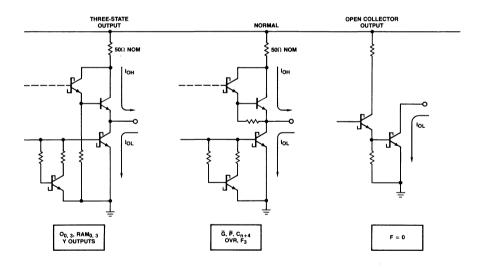

- Y<sub>0-3</sub> The four data outputs. These are three-state output lines. When enabled, they display either the four outputs of the ALU or the data on the A-port of the register stack, as determined by the destination code I<sub>678</sub>.

- OE Output Enable. When OE is HIGH, the Youtputs are OFF; when OE is LOW, the Y outputs are active (HIGH or LOW).

- G, P The carry generate and propagate outputs of the internal ALU. These signals are used with the 2902A for carry-lookahead.

- OVR Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit.

- ${f F}={f 0}$  This is an open collector output which goes HIGH (OFF) if the data on the four ALU outputs  ${f F}_{0-3}$  are all LOW. In positive logic, it indicates the result of an ALU operation is zero.

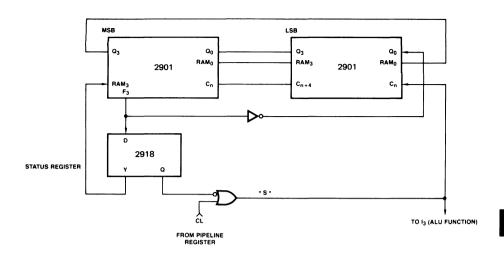

- F<sub>3</sub> The most significant ALU output bit.

- C<sub>n</sub> The carry-in to the internal ALU.

- $\mathbf{C}_{n+4}$  The carry-out of the internal ALU.

- CP The clock input. The Q register and register stack outputs change on the clock LOW-to-HIGH transition. The clock LOW time is internally the write enable to the 16 x 4 RAM which compromises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.

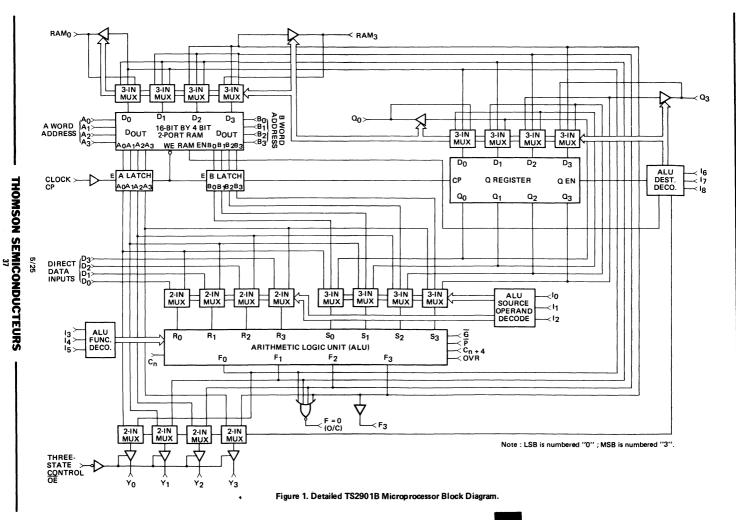

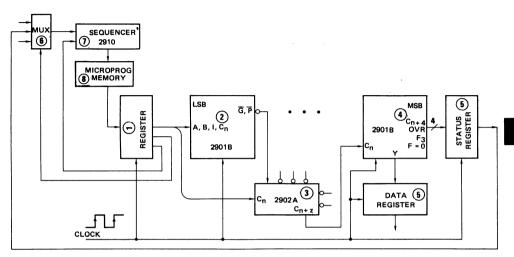

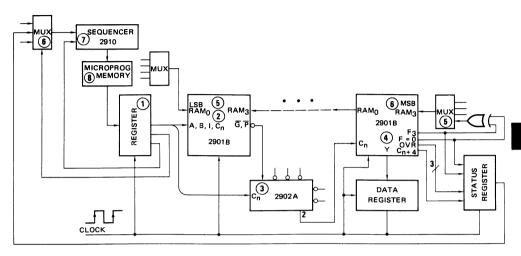

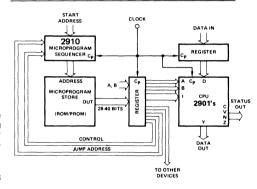

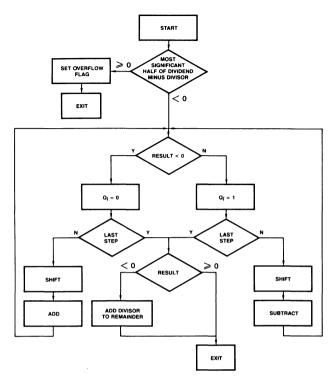

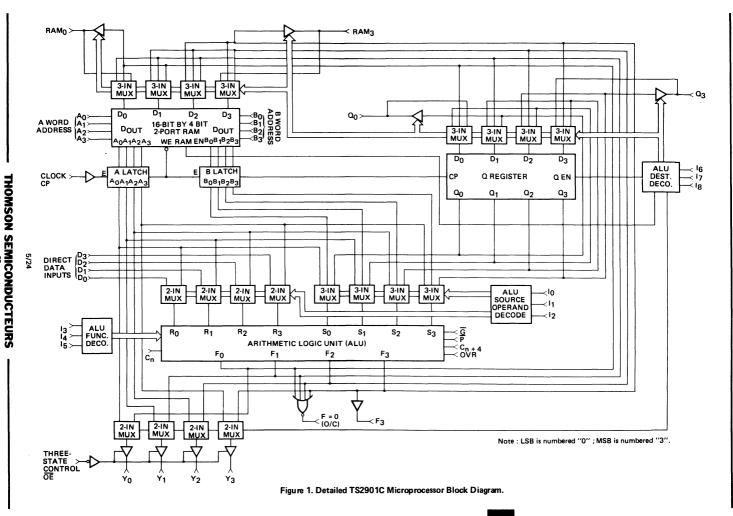

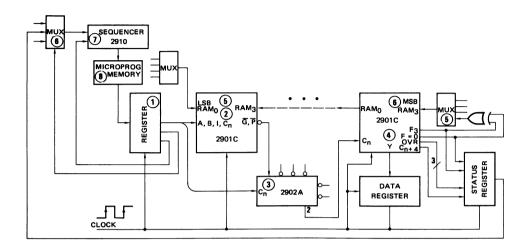

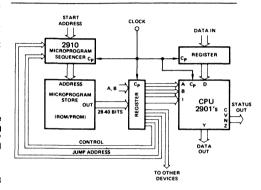

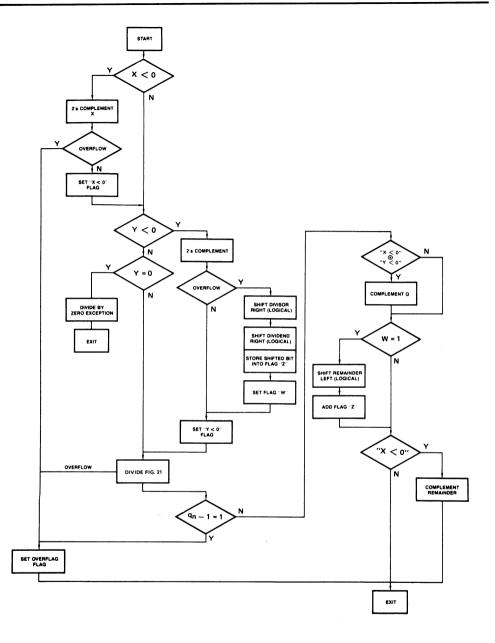

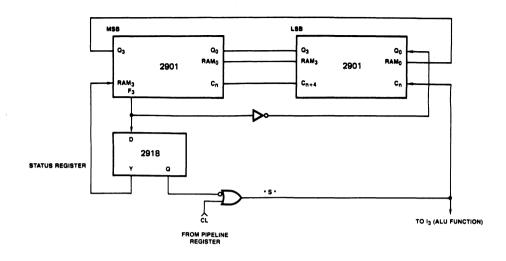

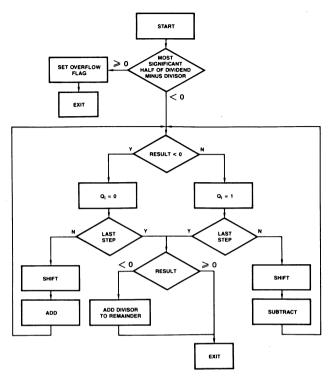

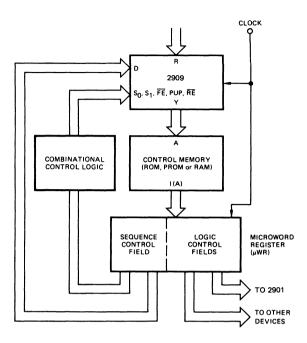

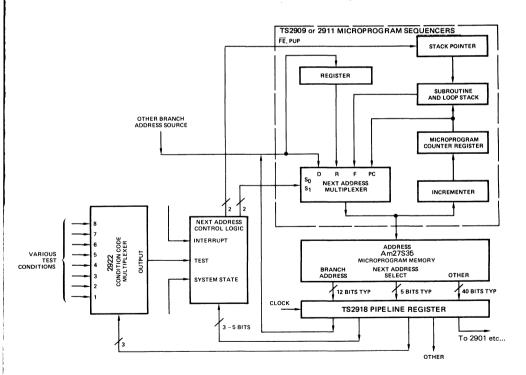

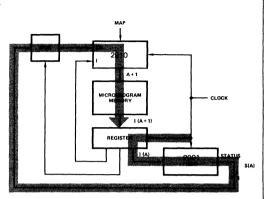

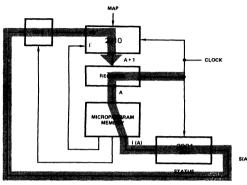

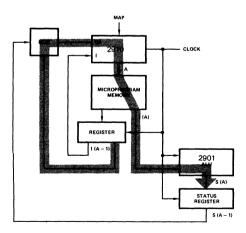

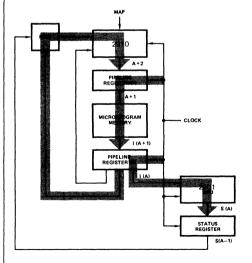

#### **ARCHITECTURE**

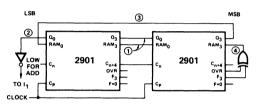

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a four-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 1, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

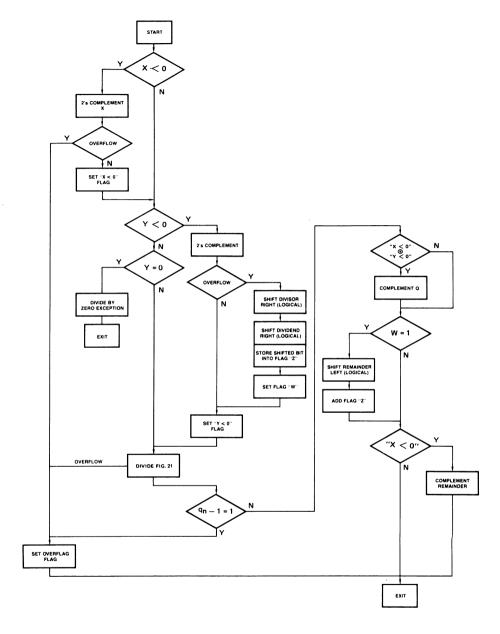

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, AO, BD, BQ, BO, DQ, DO and QO, ti is apparent that AD, AQ and AO are somewhat redundant with BD, BQ and BO in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The 2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the IQ, I1, and I2 for the eight source operand combinations are as shown in Figure 2. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The  $I_3$ ,  $I_4$ , and  $I_5$  microinstruction inputs are used to select the

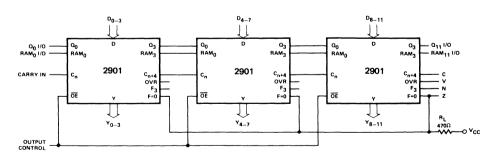

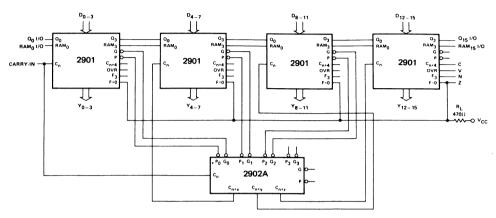

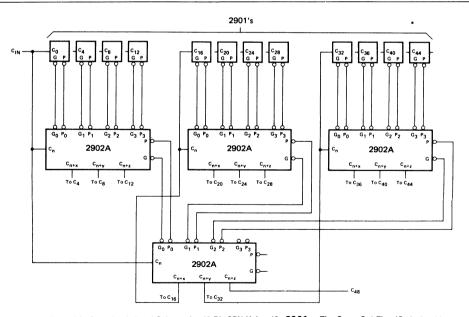

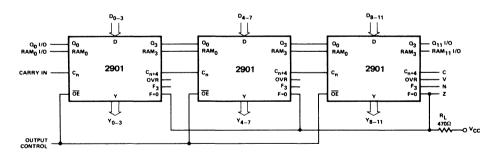

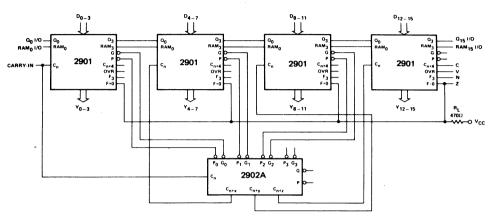

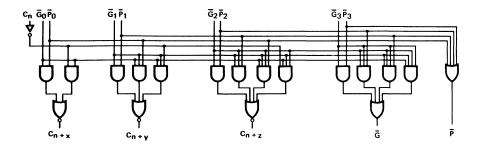

ALU function. The definition of these inputs is shown in Figure 3. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate,  $\overline{G}$ , and carry propagate,  $\overline{P}$ , are outputs of the device for use with a carry-look-ahead-generator such as the 2902A. A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in  $(C_n)$  and carry-out  $(C_{n+4})$  are active HIGH.

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F=0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices. F=0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the  $1_6$ ,  $1_7$ , and  $1_8$  microinstruction inputs. These combinations are shown in Figure 4.

The four-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control  $(\overline{OE})$  is used to enable the three-state outputs. When  $\overline{OE}$  is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the  $1_6$ ,  $1_7$ , and  $1_8$  microinstruction inputs. Refer to Figure 4 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position (÷2). The shifter has two ports; one is labeled RAM<sub>0</sub> and the other is labeled RAM<sub>3</sub>. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RAM<sub>3</sub> buffer is enabled and the RAM<sub>0</sub> multiplexer input is enabled. Likewise, in the shift down mode, the RAM<sub>0</sub> buffer and RAM<sub>3</sub> input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the I<sub>6</sub>, I<sub>7</sub> and I<sub>8</sub> microinstruction inputs as defined in Figure 4.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $I_{\hat{\mathbf{g}}}$ ,  $I_{\mathbf{7}}$ , and  $I_{\mathbf{8}}$  as shown in Figure 4.

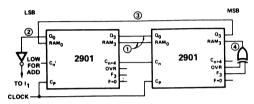

The clock input to the 2901 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

|          |                | MICR           | о со           | DE            |   | OURCE<br>ANDS |

|----------|----------------|----------------|----------------|---------------|---|---------------|

| Mnemonic | I <sub>2</sub> | I <sub>1</sub> | I <sub>O</sub> | Octal<br>Code | R | s             |

| AQ       | L              | L              | L              | 0             | Α | a             |

| AB       | L              | L              | н              | 1             | A | В             |

| ZQ       | L              | н              | L              | 2             | 0 | Q             |

| ZB       | L              | н              | н              | 3             | О | В             |

| ZA       | н              | L              | L              | 4             | О | A             |

| DA       | н              | L              | н              | 5             | D | A             |

| DQ       | н              | н              | L              | 6             | D | a             |

| DZ       | н              | н              | н              | 7             | D | 0             |

|          |                | MICRO CODE |                |               | ALU        | 01/4501          |

|----------|----------------|------------|----------------|---------------|------------|------------------|

| Mnemonic | l <sub>5</sub> | 14         | l <sub>3</sub> | Octal<br>Code | Function   | SYMBOL           |

| ADD      | L              | L          | L              | Q             | R Plus S   | R + S            |

| SUBR     | L              | L          | н              | 1             | S Minus R  | S - R            |

| SUBS     | L              | н          | L              | 2             | R Minus S  | R - S            |

| OR       | L              | н          | н              | 3             | RORS       | RVS              |

| AND      | н              | L          | L              | 4             | RANDS      | R∧S              |

| NOTRS    | н              | L          | н              | 5             | RANDS      | R∧s              |

| EXOR     | н              | н          | L              | 6             | R EX-OR S  | R₩S              |

| EXNOR    | н              | н          | Н              | 7             | R EX-NOR S | R <del>∀</del> S |

Figure 2. ALU Source Operand Control.

Figure 3. ALU Function Control.

|          |                | MICR           | о со | DE            |       | AM<br>CTION |       | REG.<br>CTION | Y      |                  | M<br>TER         | Q<br>SHIFTER    |                 |

|----------|----------------|----------------|------|---------------|-------|-------------|-------|---------------|--------|------------------|------------------|-----------------|-----------------|

| Mnemonic | l <sub>8</sub> | l <sub>7</sub> | 16   | Octal<br>Code | Shift | Load        | Shift | Load          | ООТРОТ | RAM <sub>0</sub> | RAM <sub>3</sub> | $\mathbf{a}_0$  | <b>Q</b> 3      |

| QREG     | L              | L              | L    | 0             | х     | NONE        | NONE  | F → Q         | F      | ×                | ×                | х               | ×               |

| NOP      | L              | L              | н    | 1             | х     | NONE        | ×     | NONE          | F      | ×                | ×                | х               | ×               |

| RAMA     | L              | н              | L    | 2             | NONE  | F→B         | ×     | NONE          | А      | ×                | х                | х               | ×               |

| RAMF     | L              | н              | Н    | 3             | NONE  | F → B       | ×     | NONE          | F      | ×                | ×                | X               | ×               |

| RAMQD    | н              | L              | L    | 4             | DOWN  | F/2 → B     | DOWN  | Q/2 → Q       | F      | Fo               | IN <sub>3</sub>  | Q <sub>0</sub>  | IN <sub>3</sub> |

| RAMD     | Н              | L              | н    | 5             | DOWN  | F/2 → B     | ×     | NONE          | F      | F <sub>0</sub>   | IN <sub>3</sub>  | Q <sub>0</sub>  | ×               |

| RAMQU    | н              | н              | L    | 6             | UP    | 2F → B      | UP    | 2Q → Q        | F      | IN <sub>0</sub>  | F <sub>3</sub>   | IN <sub>0</sub> | Q <sub>3</sub>  |

| RAMU     | Н              | н              | н    | 7             | UP    | 2F → B      | ×     | NONE          | F      | IN <sub>0</sub>  | F <sub>3</sub>   | ×               | Q <sub>3</sub>  |

X = Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state B = Register Addressed by B inputs.

Figure 4. ALU Destination Control.

| 0/      | 210 OCTAL                        | 0            | 1         | 2     | 3     | 4     | 5            | 6         | 7     |

|---------|----------------------------------|--------------|-----------|-------|-------|-------|--------------|-----------|-------|

| OCT 4 3 | ALU<br>Source<br>ALU<br>Function | Α, Q         | А, В      | ο, α  | О, В  | O, A  | D, A         | D, Q      | D, O  |

| 0       | C <sub>n</sub> = L<br>R Plus S   | A + Q        | A + B     | a     | В     | Α     | D + A        | D + Q     | D     |

| ١       | C <sub>n</sub> = H               | A+Q+1        | A + B + 1 | Q + 1 | B + 1 | A + 1 | D + A + 1    | D + Q + 1 | D + 1 |

| 1       | C <sub>n</sub> = L<br>S Minus R  | Q-A-1        | B-A-1     | Q-1   | B-1   | A-1   | A-D-1        | Q-D-1     | -D-1  |